Data Sheet, DS 1, Oct. 2001

# SIUC-BA Single Chip ISDN USB Controller - Basic PSB 2155 Version 1.3

Wired Communications

Never stop thinking.

Edition 2001-10-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# SIUC-BA Single Chip ISDN USB Controller - Basic PSB 2155 Version 1.3

Wired Communications

Never stop thinking.

#### PSB 2155

| Revision H        | listory: | 2001-10-01                         | DS 1 |

|-------------------|----------|------------------------------------|------|

| Previous Version: |          | None                               |      |

| Page Subjects (r  |          | major changes since last revision) |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

|                   |          |                                    |      |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Page |

|------|

|------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.4.1                                                                                                                                                                                                                                      | Overview<br>Features<br>Logic Symbol<br>Typical Application<br>Functional Description<br>Functional Block Diagram                                                                                                                                                                                                       | 2<br>4<br>5<br>6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1                                                                                                                                                                                                                                                                    | Pin Description           Pin States in Operating Modes                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

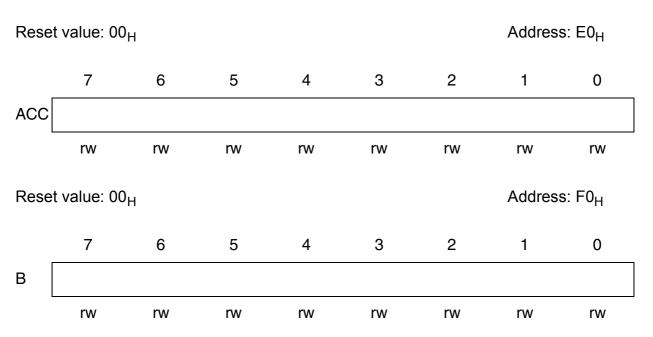

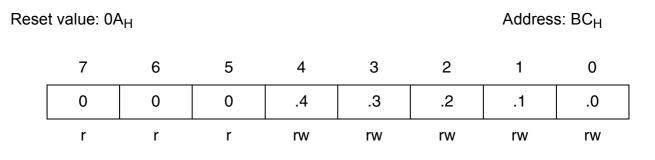

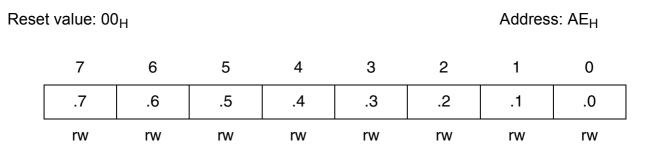

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.5.8<br>3.5.9<br>3.5.10<br>3.5.12<br>3.5.13<br><b>4</b> | WCON - WakeUp Control Register4HCON - Hardware Configuration Register4PLCONA/B - PLL Configuration Registers A, B4ACC / B - Accumulator / B Register4PSIZ - Program RAM Size Register4DSIZ - Data RAM Size Register4SYSCON1 - System Control Register 15SYSCON2 - System Control Register 25XPAGE - XRAM Page Register5 | 180       222       222       233       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       333       34       44       44       44       44       44       44       44       44       44       44       44       44       44 |

| <b>4</b><br>4.1                                                                                                                                                                                                                                                                    | USB Module                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### **Table of Contents**

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.3<br>4.4<br>4.5<br>4.6<br>4.6.1<br>4.6.2<br>4.6.3<br>4.7<br>4.8<br>4.8.1<br>4.8.2<br>4.9<br>4.9,1 | Memory Buffer Modes<br>Overview<br>Single Buffer Mode<br>Dual Buffer Mode<br>Buffer Underrun / Overflow<br>Memory Buffer Organisation<br>Memory Buffer Address Generation<br>USB Initialization<br>USB Initialization<br>USB Device Framework<br>Enumeration Process<br>Control Transfers<br>Standard Device Requests<br>Onchip USB Transceiver<br>Detach / Attach Detection and USB Power Modes<br>Self-Powered Mode<br>Bus-Powered Mode<br>USB Registers<br>GESR- Global Endpoint Stall Register | 55<br>57<br>62<br>68<br>69<br>71<br>72<br>74<br>74<br>74<br>75<br>78<br>80<br>80<br>80<br>80 |

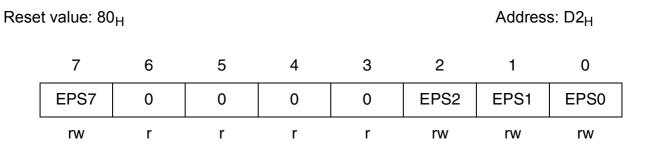

| 4.9.2                                                                                                                                          | EPSEL - Endpoint Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| 4.9.3                                                                                                                                          | IFCSEL - Interface Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 4.9.4                                                                                                                                          | USBVAL - USB Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 4.9.5                                                                                                                                          | ADROFF - Address Offset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| 4.9.6                                                                                                                                          | CIAR - Configuration Request Register                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 4.9.7                                                                                                                                          | DCR - Device Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 4.9.8                                                                                                                                          | DPWDR - Device Power Down Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 4.9.9                                                                                                                                          | FNRH / FNRL - Frame Number Register High / Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 4.9.10                                                                                                                                         | DGSR - Device Get_Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

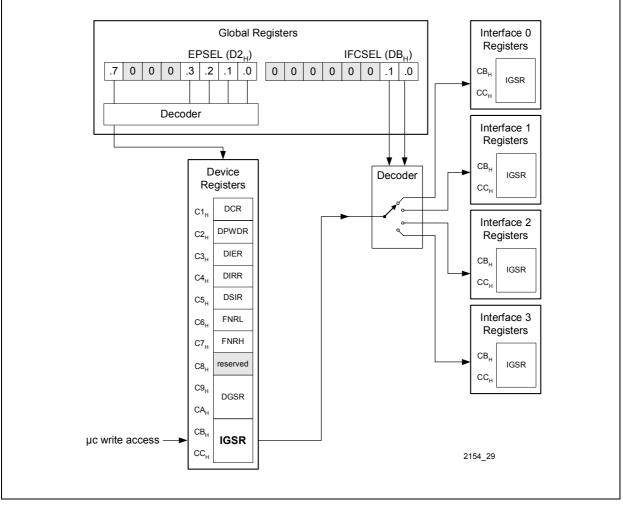

| 4.9.11                                                                                                                                         | IGSR - Interface Get_Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| 4.9.12                                                                                                                                         | EPBCn - Endpoint Buffer Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97                                                                                           |

| 4.9.13                                                                                                                                         | EPBSn - Endpoint Buffer Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98                                                                                           |

| 4.9.14                                                                                                                                         | EPBAn - Endpoint Base Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 4.9.15                                                                                                                                         | EPLENn - Endpoint Buffer Length Register                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101                                                                                          |

| 4.9.16                                                                                                                                         | EGSR - Endpoint Get_Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 102                                                                                          |

| <b>5</b><br>5.1<br>5.1.1                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103<br>103<br>104                                                                            |

| 5.1.2                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 106                                                                                          |

| 5.2                                                                                                                                            | S/T-Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107                                                                                          |

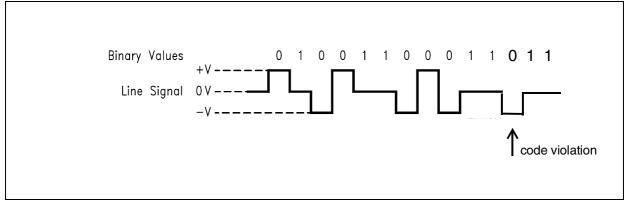

| 5.2.1                                                                                                                                          | S/T-Interface Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109                                                                                          |

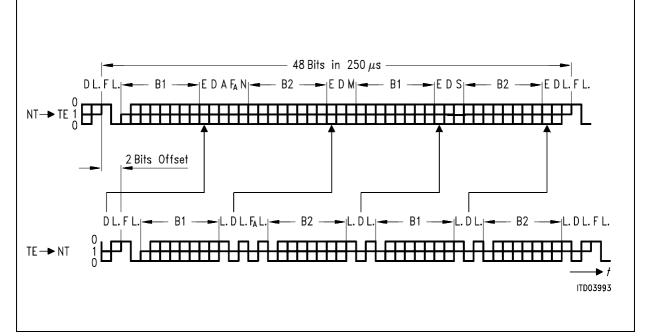

| 5.2.2                                                                                                                                          | S/T-Interface Multiframing                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 111                                                                                          |

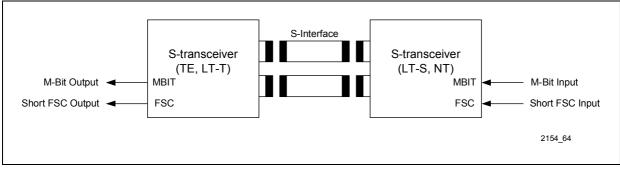

| 5.2.3                                                                                                                                          | Multiframe Synchronization (M-Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 5.2.4                                                                                                                                          | Data Transfer and Delay between IOM-2 and S/T                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 114                                                                                          |

#### **Table of Contents**

| Page |

|------|

|------|

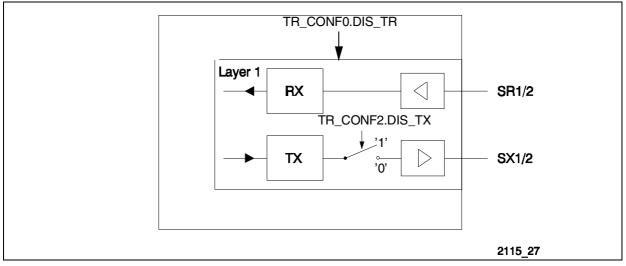

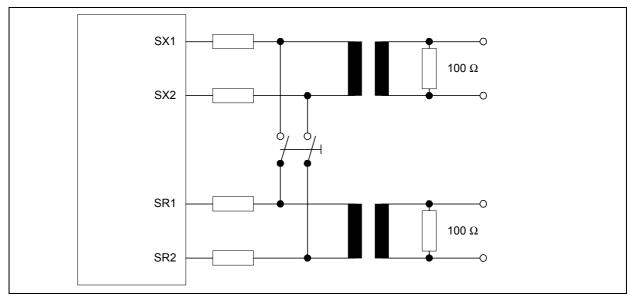

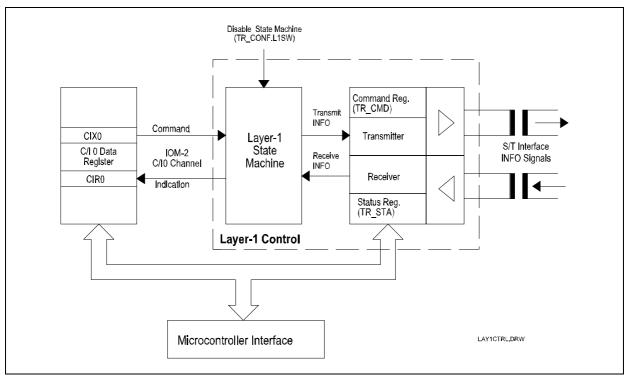

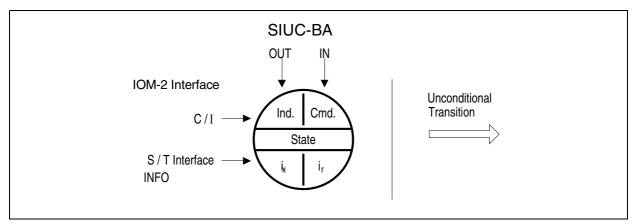

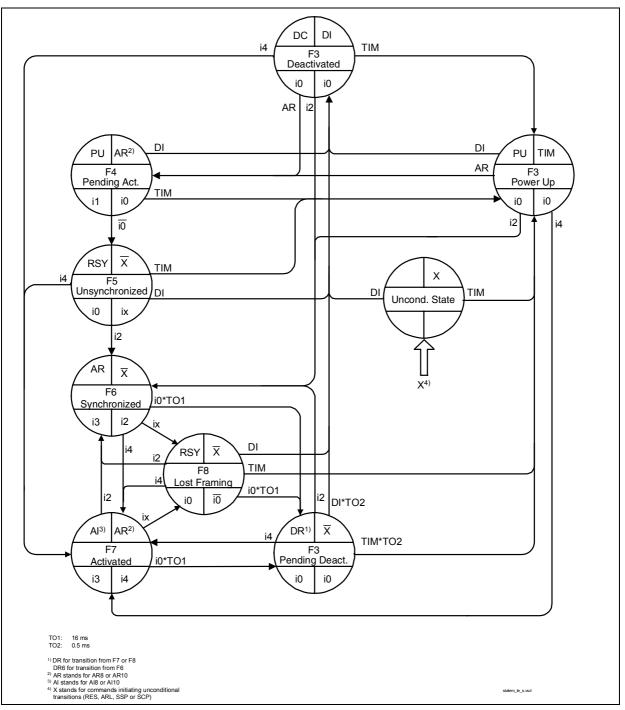

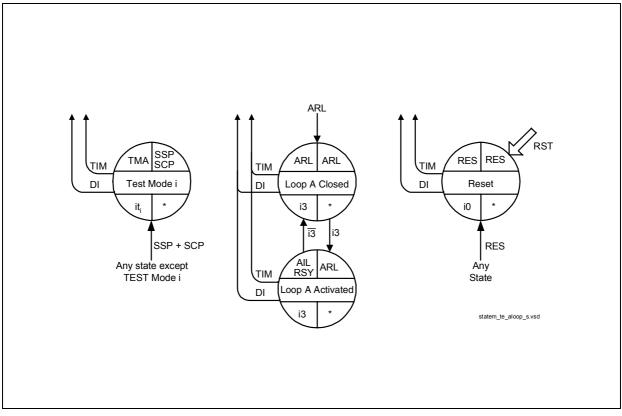

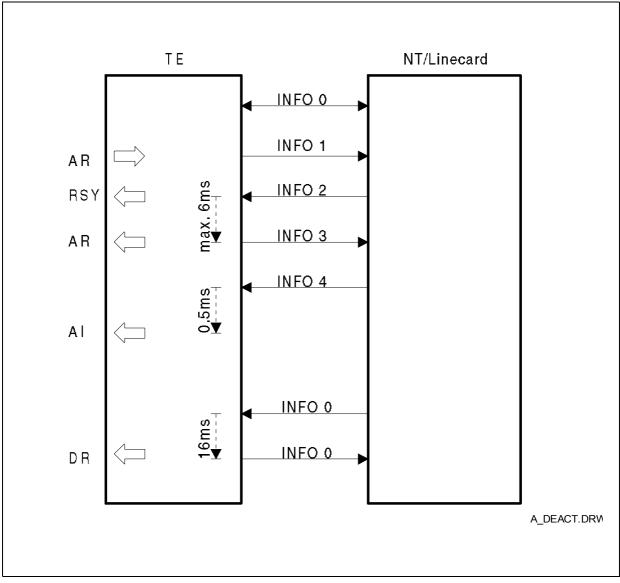

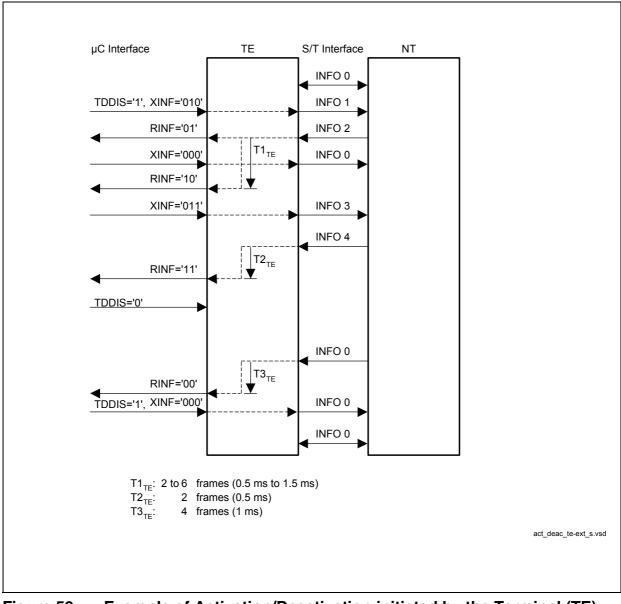

| 5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11<br>5.3<br>5.3.1<br>5.3.2<br>5.4<br>5.4.1<br>5.4.2 | Transmitter Characteristics<br>Receiver Characteristics<br>S/T Interface Circuitry<br>S/T Interface Delay Compensation<br>Level Detection Power Down<br>Transceiver Enable/Disable<br>Test Functions<br>Control of Layer-1<br>State Machine TE Mode<br>Command/ Indicate Channel Codes (C/I0) - Overview<br>Control Procedures<br>Example of Activation/Deactivation<br>Activation initiated by the Terminal | <ol> <li>117</li> <li>118</li> <li>120</li> <li>120</li> <li>121</li> <li>121</li> <li>123</li> <li>126</li> <li>132</li> <li>133</li> <li>133</li> <li>134</li> </ol> |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4.3                                                                                                           | Activation initiated by the Network Termination NT                                                                                                                                                                                                                                                                                                                                                           | 135                                                                                                                                                                    |

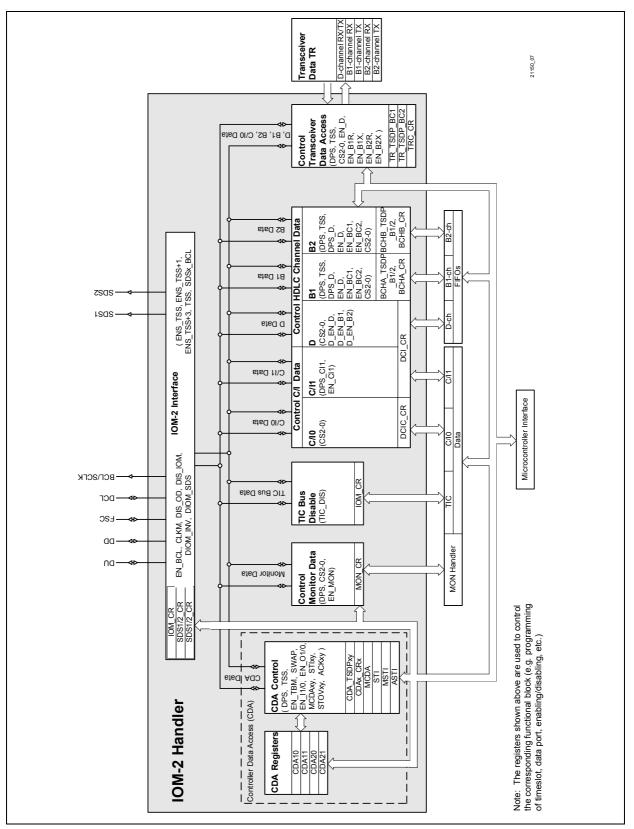

| 5.5                                                                                                             | IOM-2 Interface                                                                                                                                                                                                                                                                                                                                                                                              | 136                                                                                                                                                                    |

| 5.5.1                                                                                                           | IOM-2 Handler                                                                                                                                                                                                                                                                                                                                                                                                | 138                                                                                                                                                                    |

| 5.5.2                                                                                                           | IDSL Support                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                        |

| 5.5.3                                                                                                           | Serial Data Strobe Signal and Strobed Data Clock                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                        |

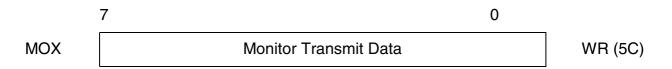

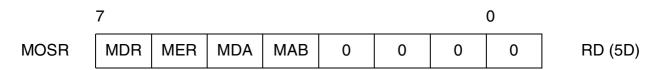

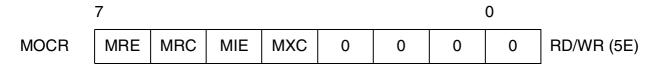

| 5.5.4                                                                                                           | IOM-2 Monitor Channel                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                        |

| 5.5.5                                                                                                           | C/I Channel Handling                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                        |

| 5.5.6                                                                                                           | D-Channel Access Control                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                        |

| 5.5.7                                                                                                           | Activation/Deactivation of IOM-2 Interface                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 5.6                                                                                                             | HDLC Controllers                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                        |

| 5.6.1                                                                                                           | Message Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                        |

| 5.6.2                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                        |

| 5.6.3                                                                                                           | Data Transmission                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                        |

| 5.6.4                                                                                                           | Access to IOM-2 channels                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                        |

| 5.6.5                                                                                                           | Extended Transparent Mode                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                        |

| 5.6.6                                                                                                           | HDLC Controller Interrupts                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 5.7                                                                                                             | Test Functions                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                        |

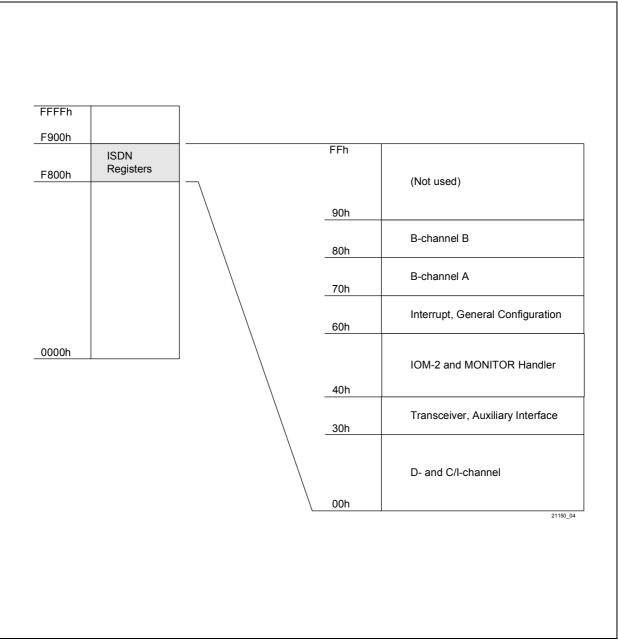

| 5.8                                                                                                             | ISDN Register Description                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                        |

| 5.8.1                                                                                                           | D-channel HDLC Control and C/I Registers                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                        |

| 5.8.2                                                                                                           | Transceiver Registers                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                        |

| 5.8.3                                                                                                           | Auxiliary Interface Registers                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                        |

| 5.8.4                                                                                                           | IOM-2 and MONITOR Handler                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                        |

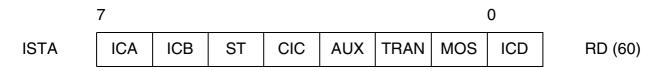

| 5.8.5                                                                                                           | Interrupt and General Configuration                                                                                                                                                                                                                                                                                                                                                                          | 252                                                                                                                                                                    |

| 5.8.6                                                                                                           | B-Channel Registers                                                                                                                                                                                                                                                                                                                                                                                          | 258                                                                                                                                                                    |

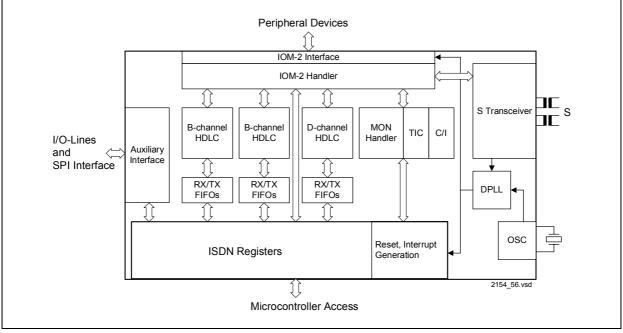

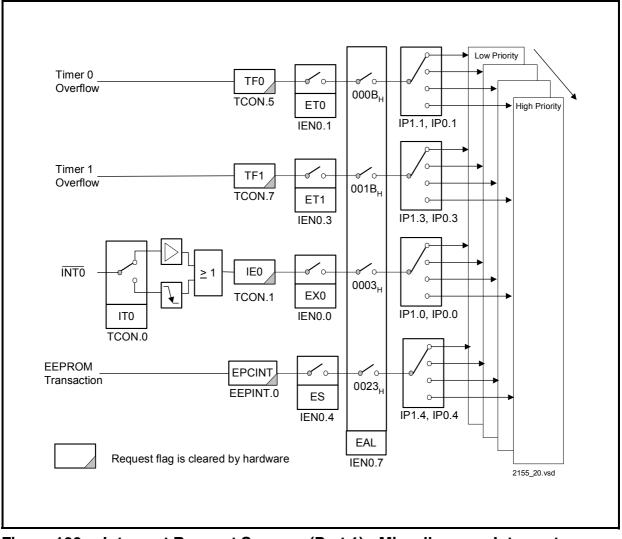

| <b>6</b><br>6.1<br>6.1.1<br>6.1.2                                                                               | Interrupt System<br>Interrupt Registers<br>Interrupt Request / Control Flags<br>Interrupt Enable Registers                                                                                                                                                                                                                                                                                                   | 275<br>275                                                                                                                                                             |

| 6.1.3                                                                                                           | Interrupt Priority                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                        |

| Table o                                                                                                    | of Contents                                                                                                                                                                                                                                                                                                                                                    | Page                                                                      |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 6.2<br>6.3                                                                                                 | Interrupt Handling                                                                                                                                                                                                                                                                                                                                             |                                                                           |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4<br>7.5 | Firmware         Firmware Operation Modes         Boot Loader Firmware         Memory Modes         Firmware Download Mode         Firmware Execution in RAM         USB Models         General USB Model in SIUC-BA         USB Model in Download Mode (DFU)         USB Model in Operational Mode (CDC)         USB Configuration Data         Remote Wakeup | 295<br>296<br>299<br>300<br>301<br>302<br>302<br>303<br>303<br>306        |

| 8<br>8.1<br>8.1.1<br>8.2<br>8.2.1<br>8.2.2<br>8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.3<br>8.3.3             | General Features         Clock Generation         USB / Microcontroller         S-Transceiver PLL         Reset Generation         Hardware Reset Operation         Software Reset         Auxiliary Interface         Mode Dependent Functions         SPI Interface         SPI Registers         Voltage Regulator                                          | 312<br>312<br>313<br>316<br>316<br>316<br>320<br>320<br>322<br>325        |

| 9<br>9.1<br>9.2.1<br>9.2.2<br>9.3<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6                    | Operational Description         Configuration of Functional Blocks         Power Saving Modes         Idle Mode         Suspend Mode         Sequence of Operations         Reset to Active         Active to Idle         Idle to Active         Active to Suspend         Suspend to Active         Interrupt Wakeup Control                                 | 329<br>329<br>331<br>331<br>333<br>337<br>337<br>338<br>338<br>339<br>339 |

| <b>10</b><br>10.1                                                                                          | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                     |                                                                           |

# **Table of Contents**

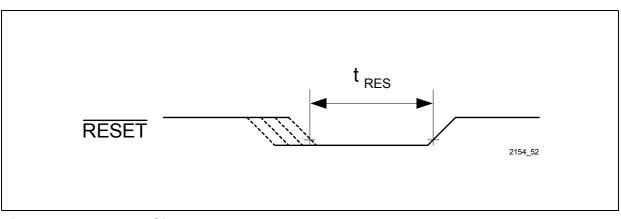

| 10.10<br>10.11<br>10.12<br><b>11</b> | SPI Interface Timing          USB Transceiver Characteristics          Reset          Package Outlines | 353<br>354 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------|------------|

| 10.9                                 | Auxiliary Interface Timing                                                                             |            |

| 10.8                                 | IOM-2 Interface Timing                                                                                 |            |

| 10.7                                 | AC Characteristics                                                                                     |            |

| 10.6                                 | Recommended Transformer Specification                                                                  | 347        |

| 10.5                                 | Oscillator Specification                                                                               | 346        |

| 10.4                                 | Capacitances                                                                                           | 345        |

| 10.3                                 | Voltage Regulator                                                                                      | 344        |

| 10.2                                 | DC Characteristics                                                                                     | 342        |

# List of Figures

# Page

| -          |                                                                  | _   |

|------------|------------------------------------------------------------------|-----|

| Figure 1   |                                                                  |     |

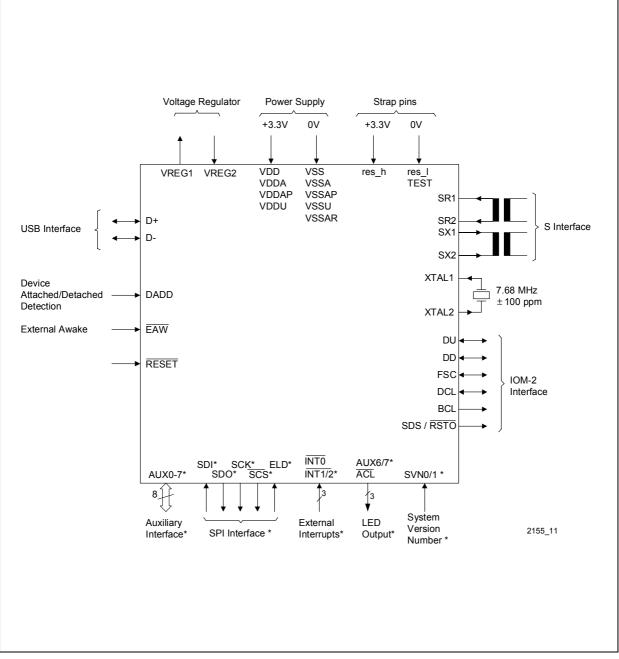

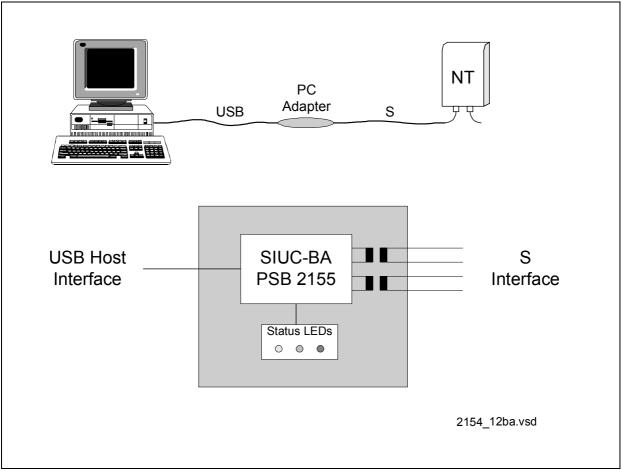

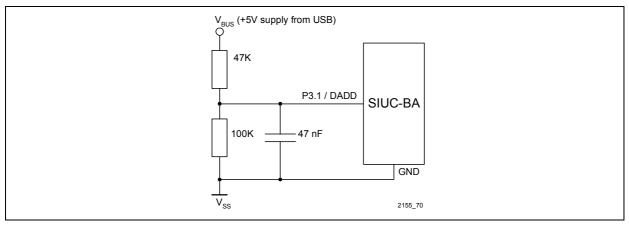

| Figure 2   | ISDN PC Adapter for S Interface                                  |     |

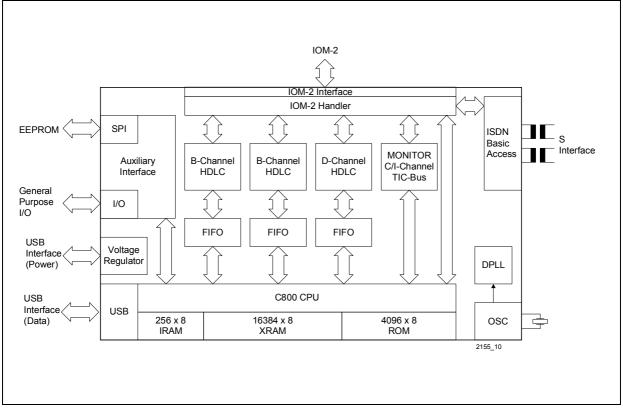

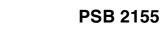

| Figure 3   | Block Diagram                                                    |     |

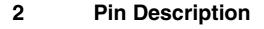

| Figure 4   | Pin Diagram                                                      |     |

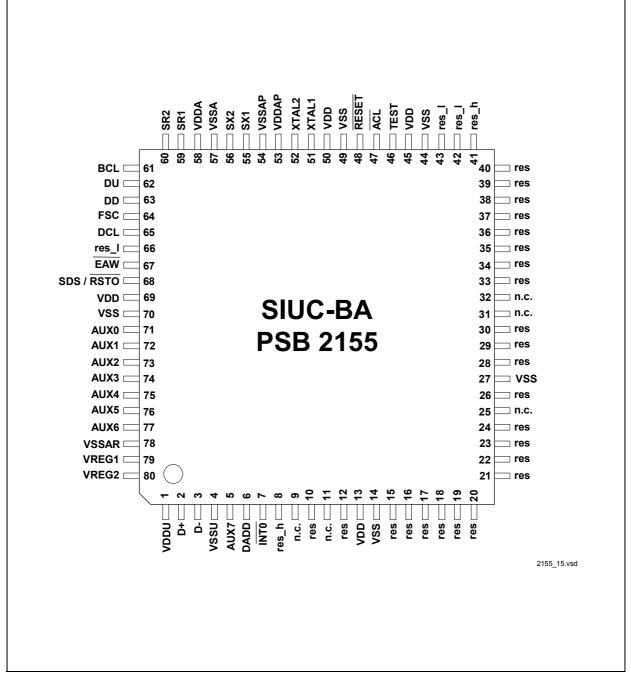

| Figure 5   | Fetch Execute Sequence.                                          |     |

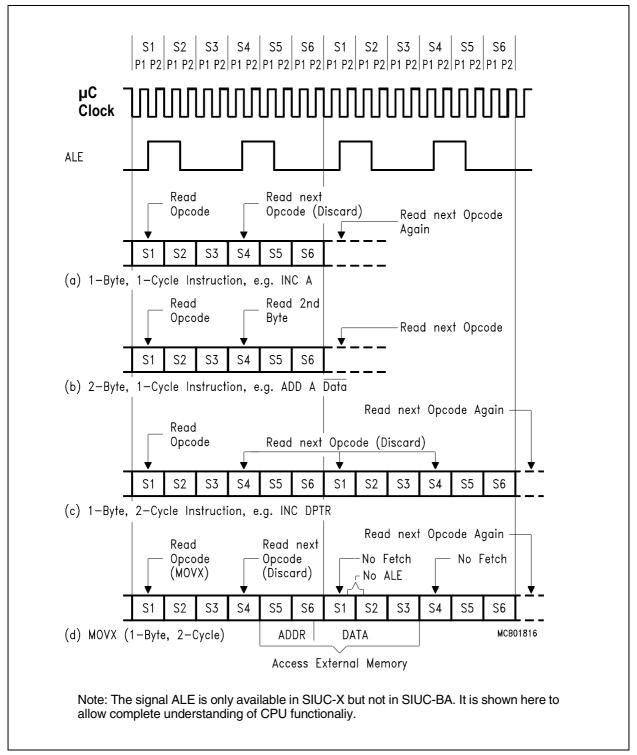

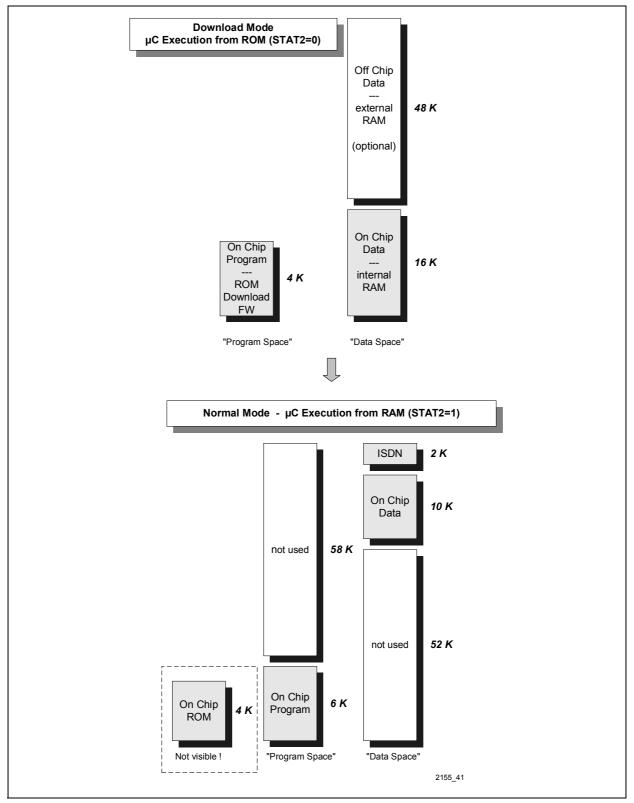

| Figure 6   | C800 Default Memory Map (Firmware Execution Mode)                |     |

| Figure 7   | Switching from Download Mode to Operational Mode                 |     |

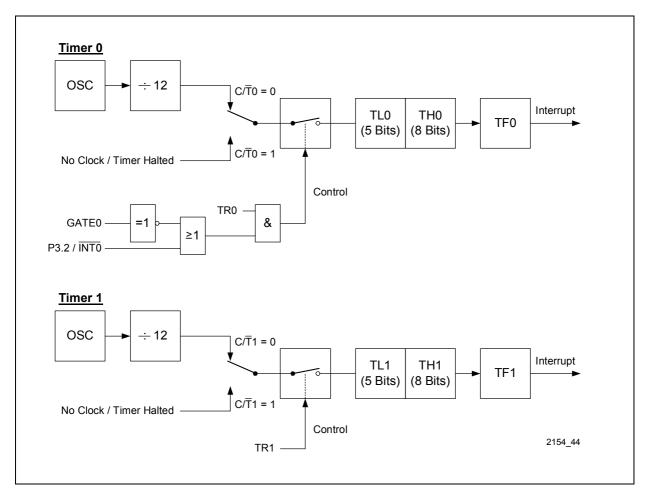

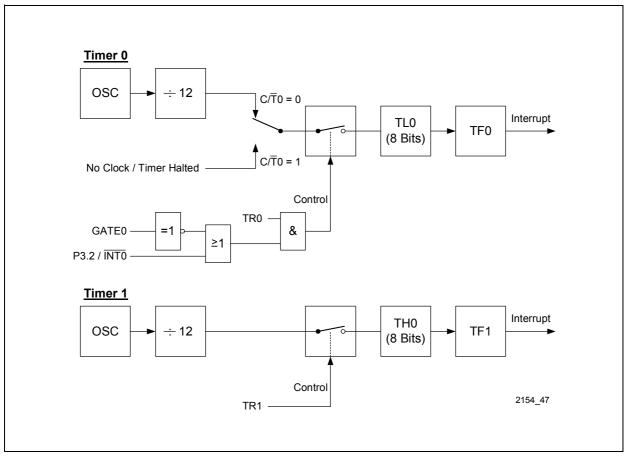

| Figure 8   | Timer Mode 0: 13-Bit Timer                                       |     |

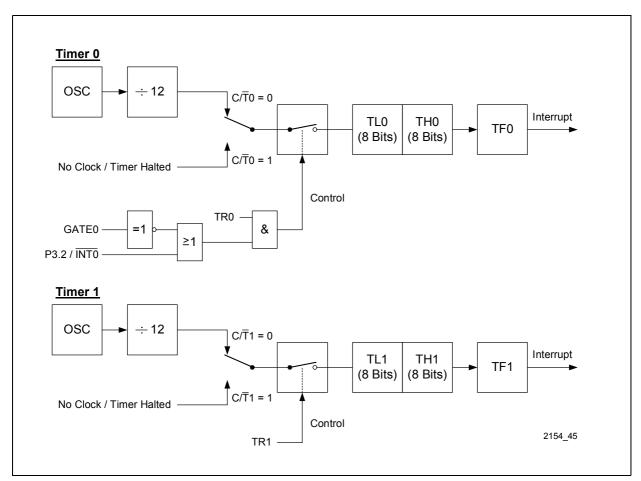

| Figure 9   | Timer Mode 1: 16-Bit Timer                                       |     |

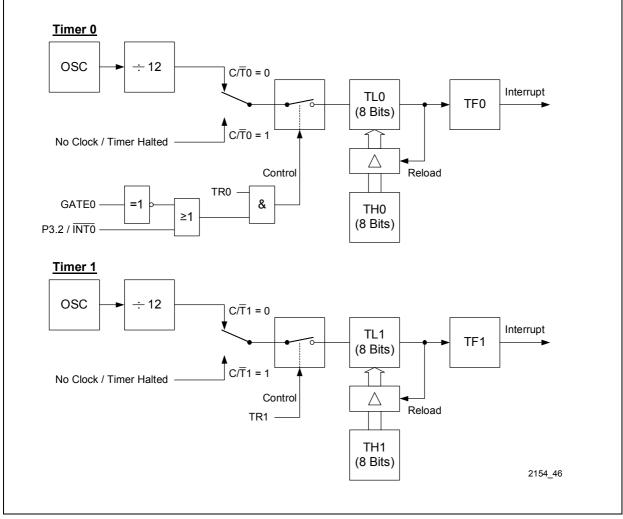

| Figure 10  | Timer Mode 2: 8-Bit Timer with Auto-Reload                       |     |

| Figure 11  | Timer Mode 3: Two 8-Bit Timers                                   | 34  |

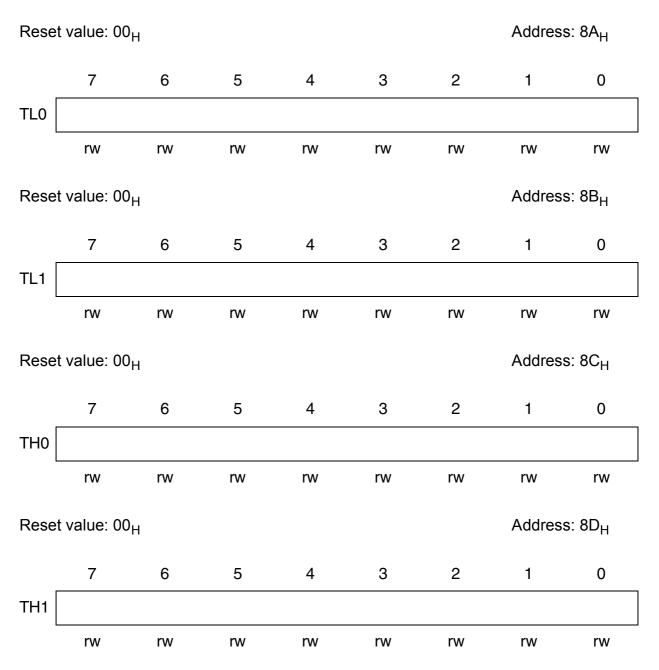

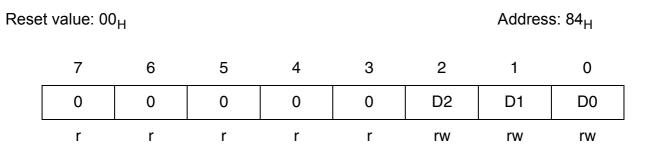

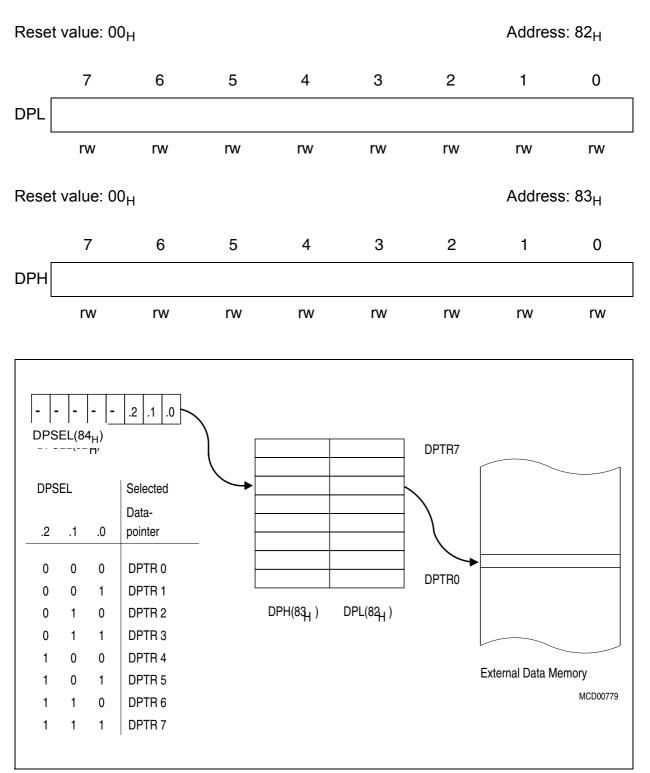

| Figure 12  | Data Memory Access via 8 data pointers                           | 40  |

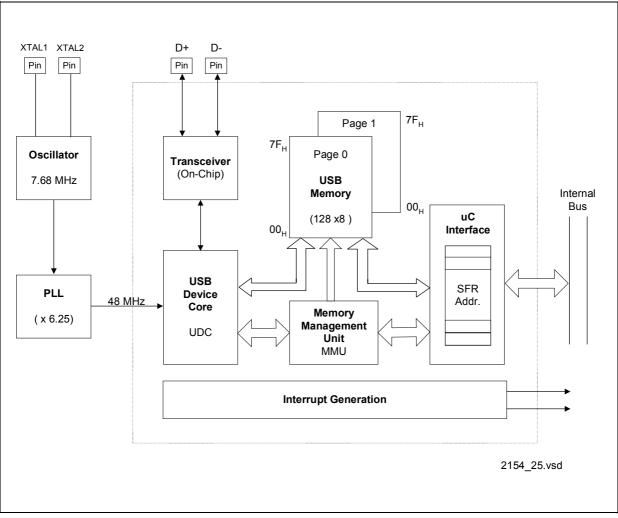

| Figure 13  | USB Module Block Diagram                                         | 53  |

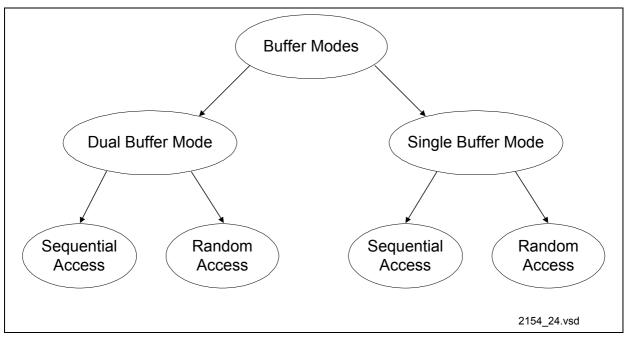

| Figure 14  | Memory Buffer Modes                                              | 55  |

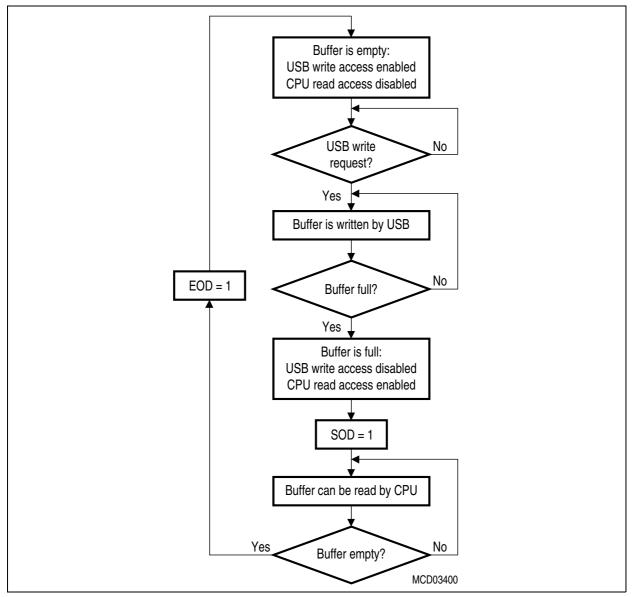

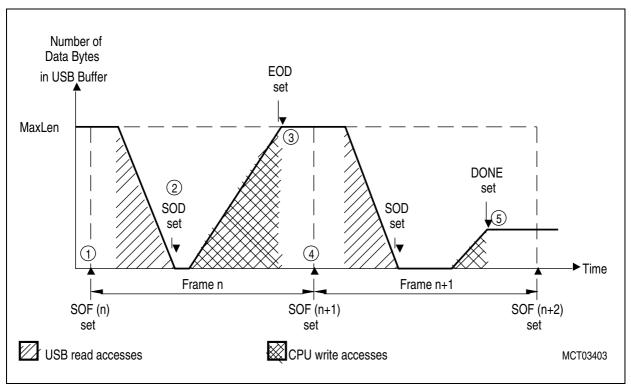

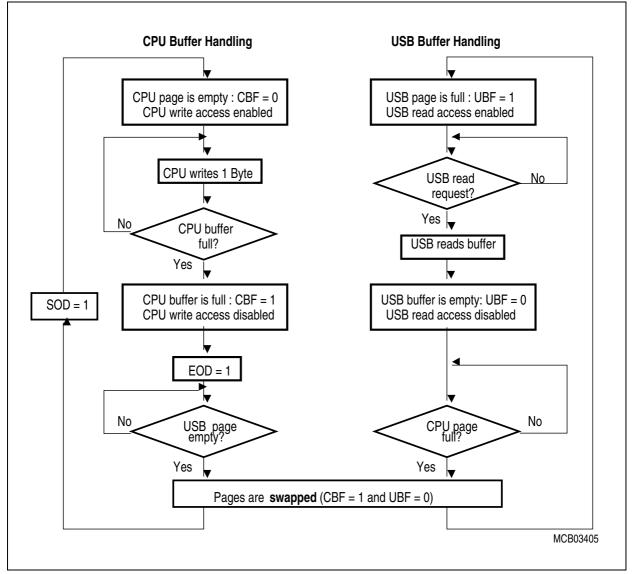

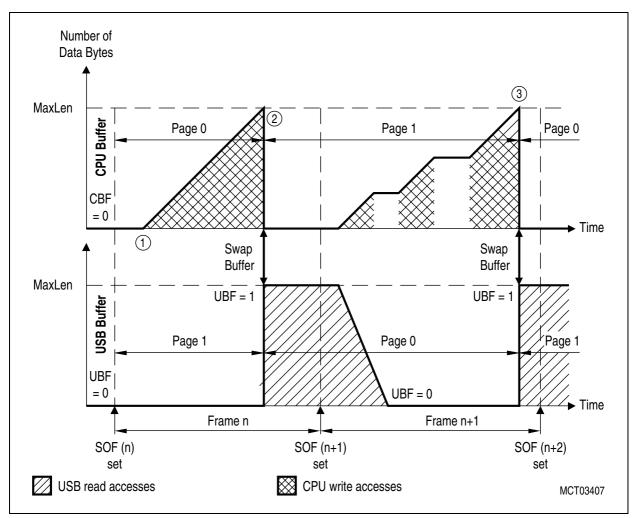

| Figure 15  | USB Write Access in Single Buffer Mode - Buffer Handling         | 57  |

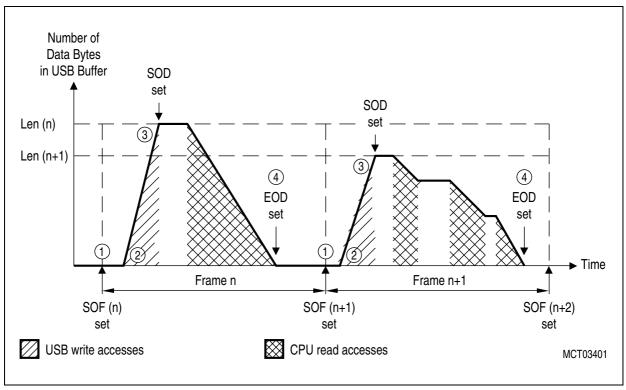

| Figure 16  | Single Buffer Mode : Standard USB Write Access                   | 58  |

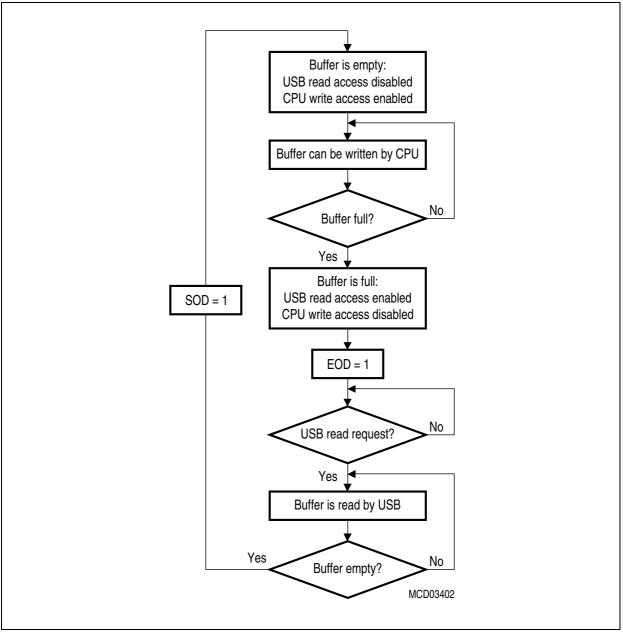

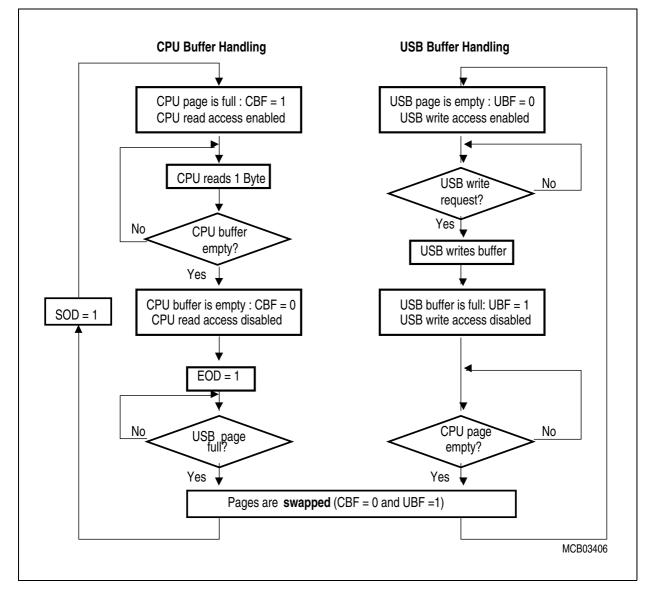

| Figure 17  | USB Read Access in Single Buffer Mode - Buffer Handling          | 59  |

| Figure 18  | Single Buffer Mode : Standard USB Read Access                    |     |

| Figure 19  | Single Buffer Mode : USB Read Access with                        |     |

| 5          | Start-of-Frame-Done Enabled                                      | 61  |

| Figure 20  | USB Read Access in Dual Buffer Mode - Buffer Handling            |     |

| Figure 21  | USB Write Access in Dual Buffer Mode - Buffer Handling           |     |

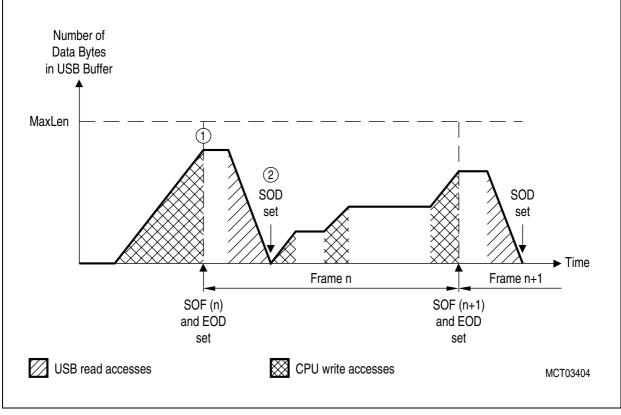

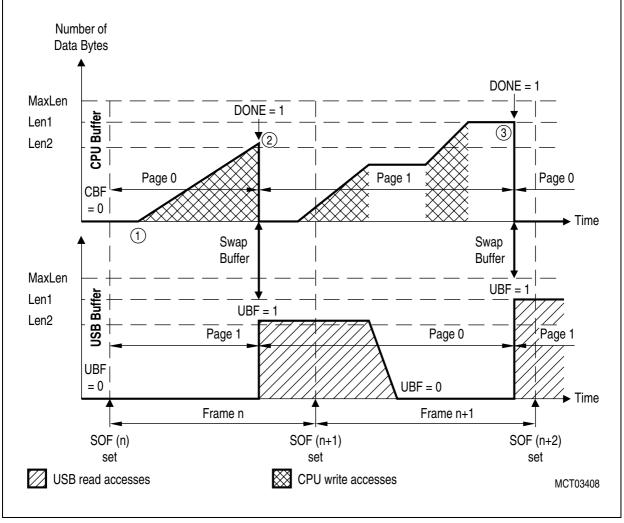

| Figure 22  | Dual Buffer Mode USB Read Access:                                |     |

|            | Buffer Switching when MaxLen is reached                          | 64  |

| Figure 23  | Dual Buffer Mode USB Read Access:                                | -   |

|            | Buffer Switching by Setting Bit DONE                             | 65  |

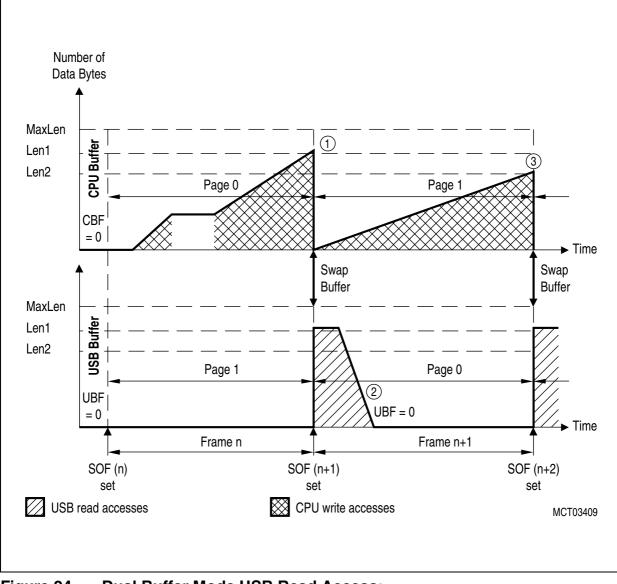

| Figure 24  | Dual Buffer Mode USB Read Access:                                | ••• |

|            | Buffer Switching on SOF with SOFDE=1                             | 66  |

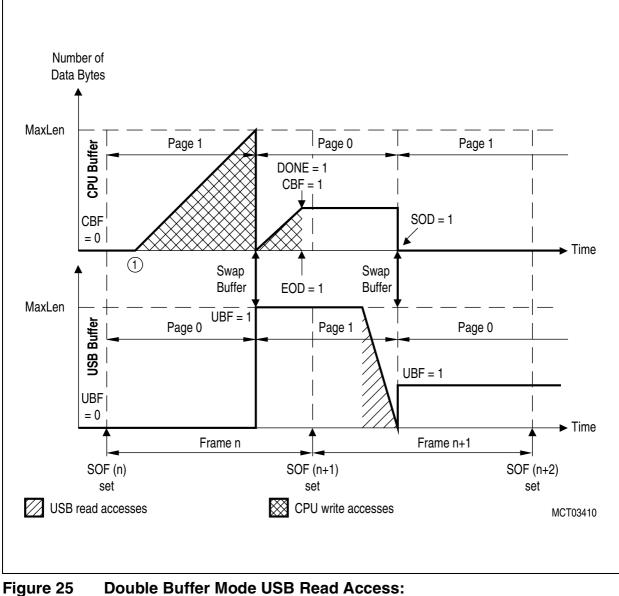

| Figure 25  | Double Buffer Mode USB Read Access:                              | 00  |

| i iguro zo | Data Length greater than Packet Length (MaxLen)                  | 67  |

| Figure 26  | Endpoint Buffer Allocation (Example: 7+1 Endpoints)              |     |

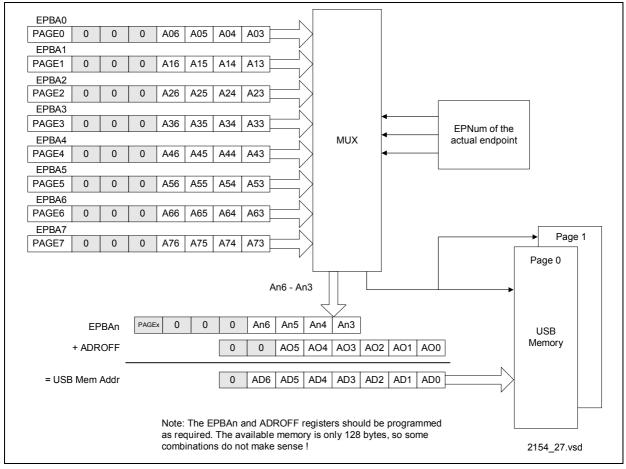

| Figure 27  | USB Memory Address Generation.                                   |     |

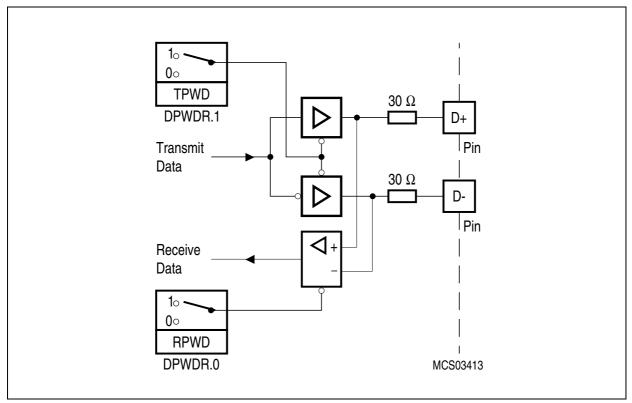

| Figure 28  | USB Onchip Driver Circuitry                                      |     |

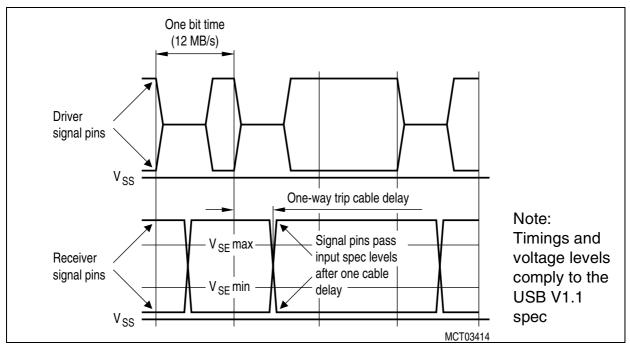

| Figure 29  | Full Speed USB Driver Signal Waveforms.                          |     |

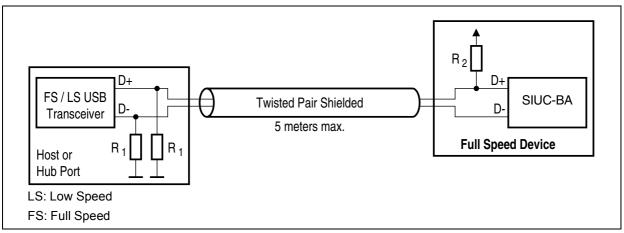

| Figure 30  | High Speed Device Cable and Resistor Connection                  |     |

| Figure 31  | Device Attached - Device Detached Detection in Self-Powered Mode |     |

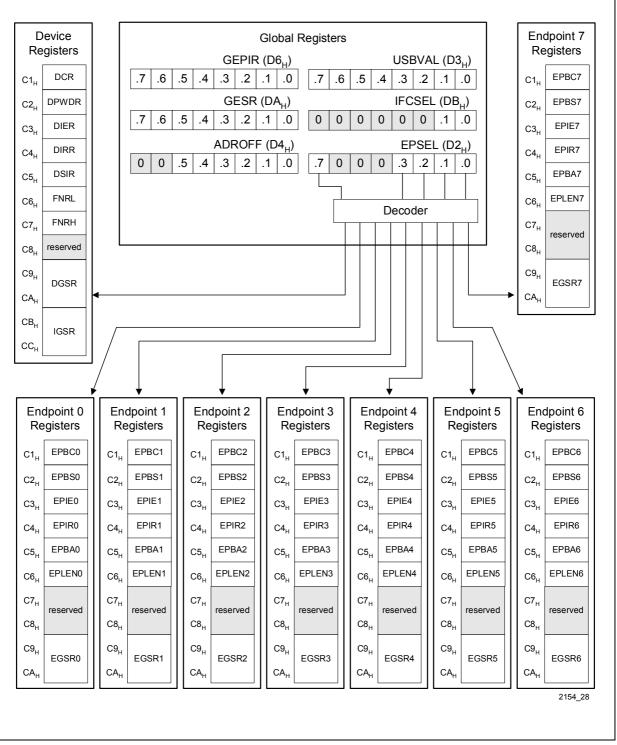

| Figure 32  | USB Register Set.                                                |     |

| •          | USB Interface Get_Status Registers                               |     |

| Figure 33  | -                                                                |     |

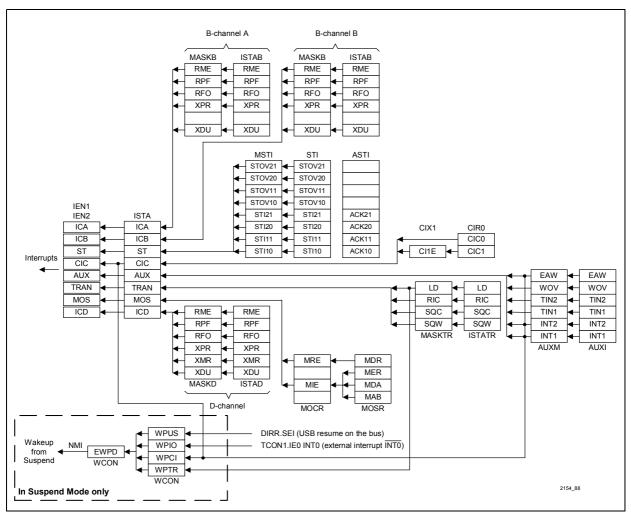

| Figure 34  | Functional Block Diagram of the ISDN Module                      |     |

| Figure 35  | 1 8                                                              | 104 |

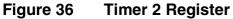

| Figure 36  | 6                                                                | 105 |

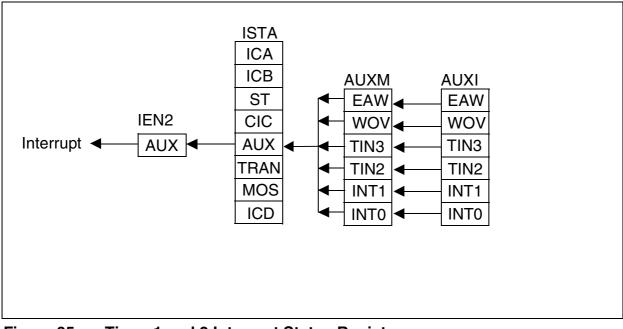

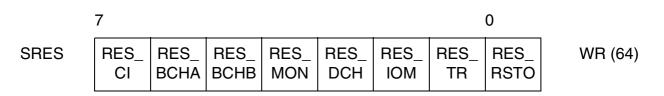

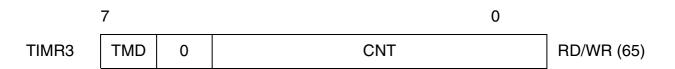

| Figure 37  | Timer 3 Register                                                 | 105 |

| List of Fig                                      | gures Pa                                                                          | ige      |

|--------------------------------------------------|-----------------------------------------------------------------------------------|----------|

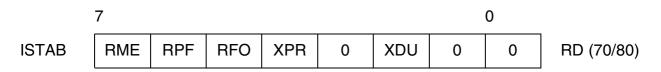

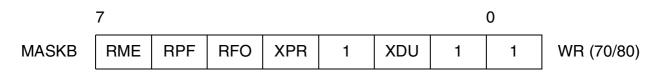

| Figure 38<br>Figure 39<br>Figure 40<br>Figure 41 | <b>o o</b>                                                                        | 06       |

| 0                                                |                                                                                   |          |

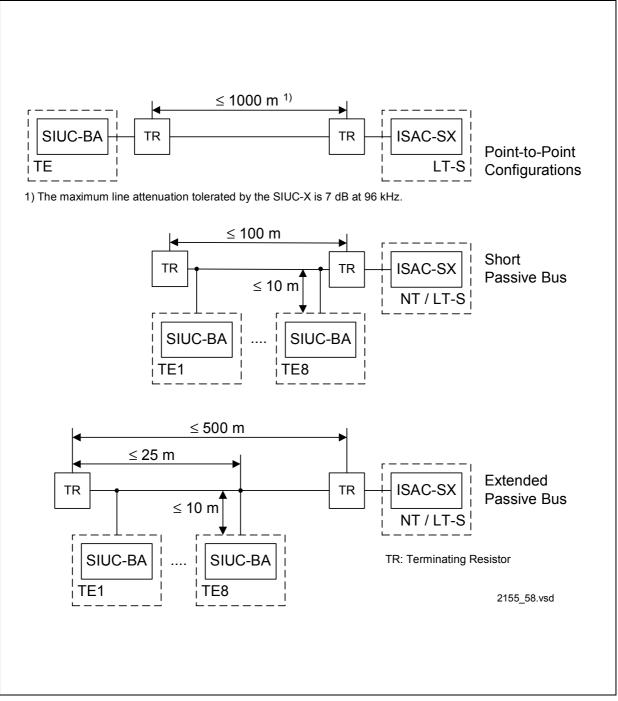

| Figure 42                                        |                                                                                   | 10       |

| Figure 43                                        |                                                                                   | 13       |

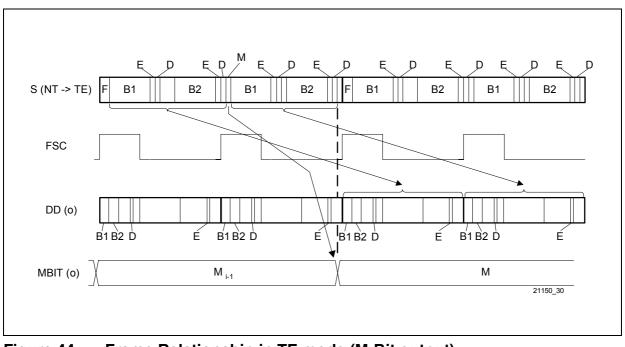

| Figure 44                                        |                                                                                   | 13       |

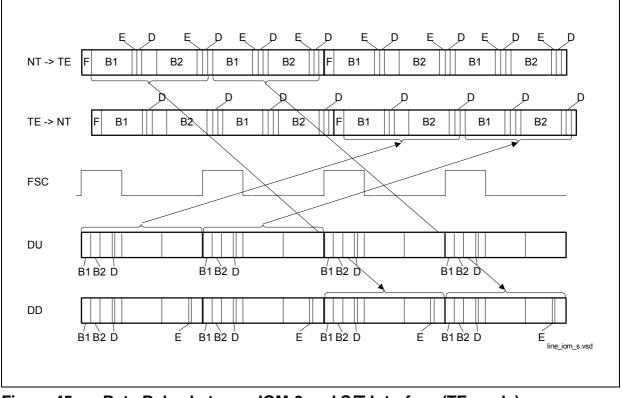

| Figure 45                                        |                                                                                   | 14<br>TE |

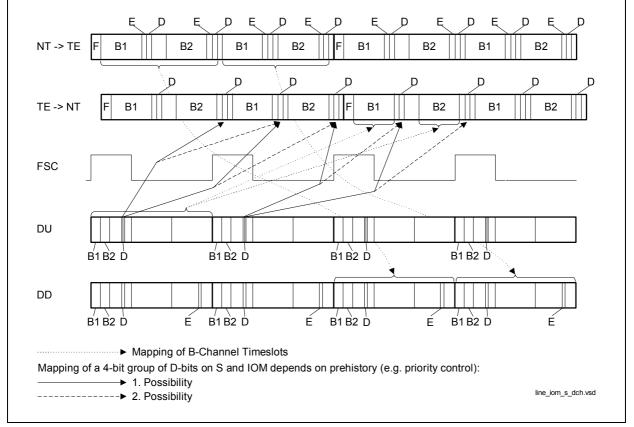

| Figure 46                                        | Data Delay between IOM-2 and S/T Interface with S/G Bit Evaluation (<br>mode) 115 |          |

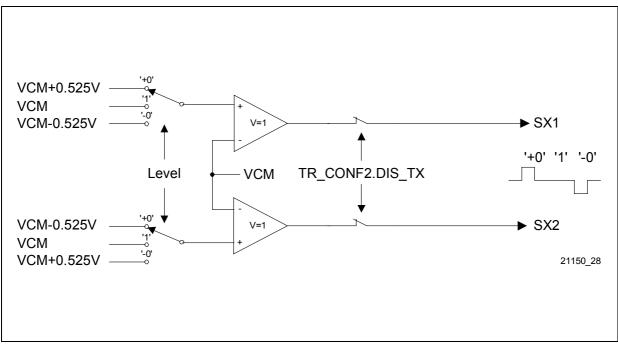

| Figure 47                                        | Equivalent Internal Circuit of the Transmitter Stage                              | 16       |

| Figure 48                                        | Equivalent Internal Circuit of the Receiver Stage                                 |          |

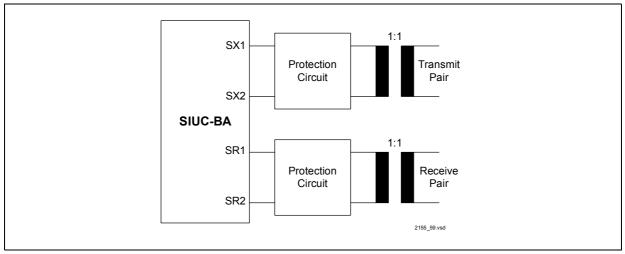

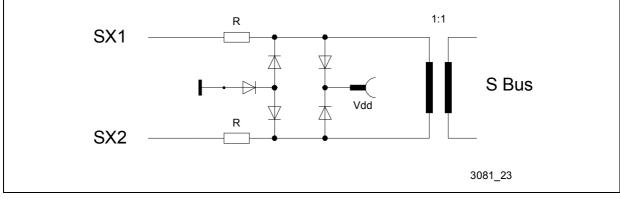

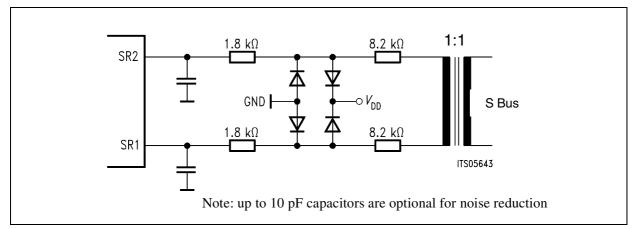

| Figure 49                                        | Connection of Line Transformers and Power Supply to the SIUC-BA 1                 |          |

| Figure 50                                        |                                                                                   | 19       |

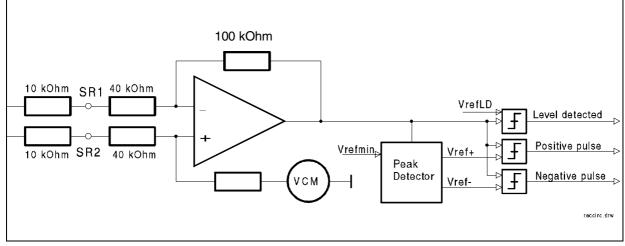

| Figure 51                                        | External Circuitry for Symmetrical Receivers                                      |          |

| Figure 52                                        |                                                                                   | 21       |

| Figure 53                                        | •                                                                                 | 22       |

| Figure 54                                        |                                                                                   | 23       |

| Figure 55                                        |                                                                                   | 24       |

| Figure 56                                        | -                                                                                 | 26       |

| Figure 57                                        |                                                                                   | 27       |

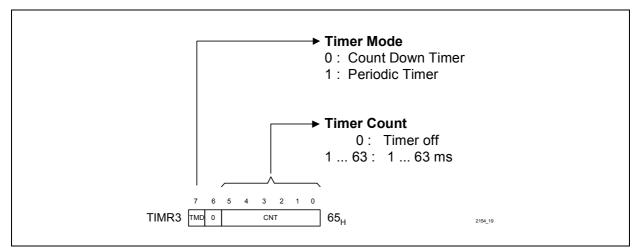

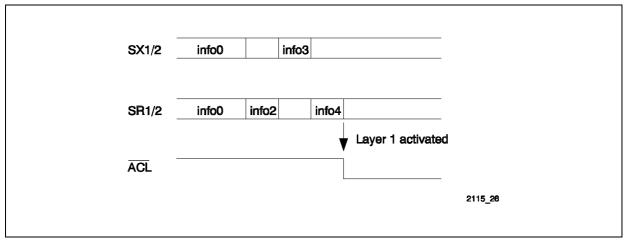

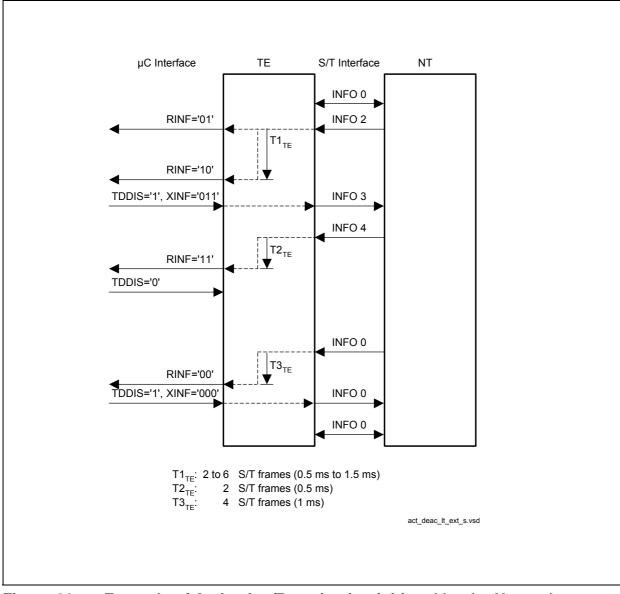

| Figure 58                                        | -                                                                                 | 33       |

| Figure 59                                        |                                                                                   |          |

| -                                                | Activation/Deactivation completely under Software Control 1                       | 34       |

| Figure 60                                        | Example of Activation/Deactivation initiated by the Network<br>Termination (NT).  |          |

|                                                  | Activation/Deactivation completely under Software Control 1                       | 35       |

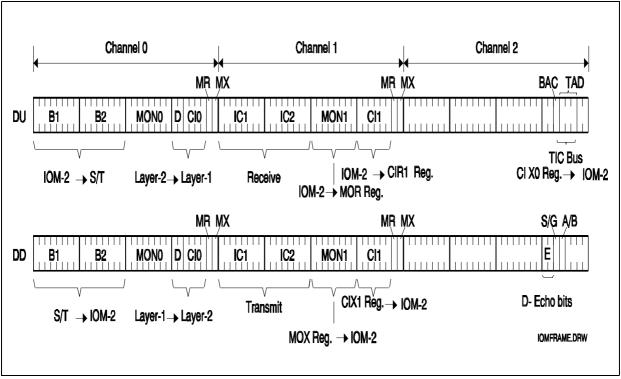

| Figure 61                                        | IOM-2 Frame Structure in Terminal Mode                                            |          |

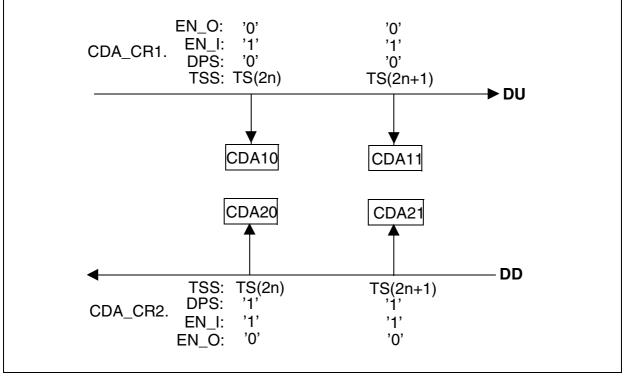

| Figure 62                                        |                                                                                   | 39       |

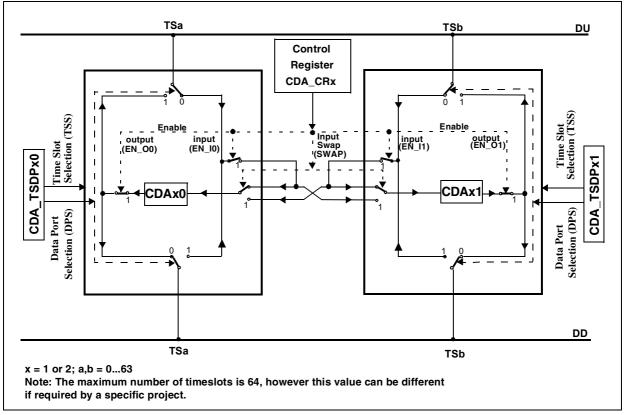

| Figure 63                                        |                                                                                   |          |

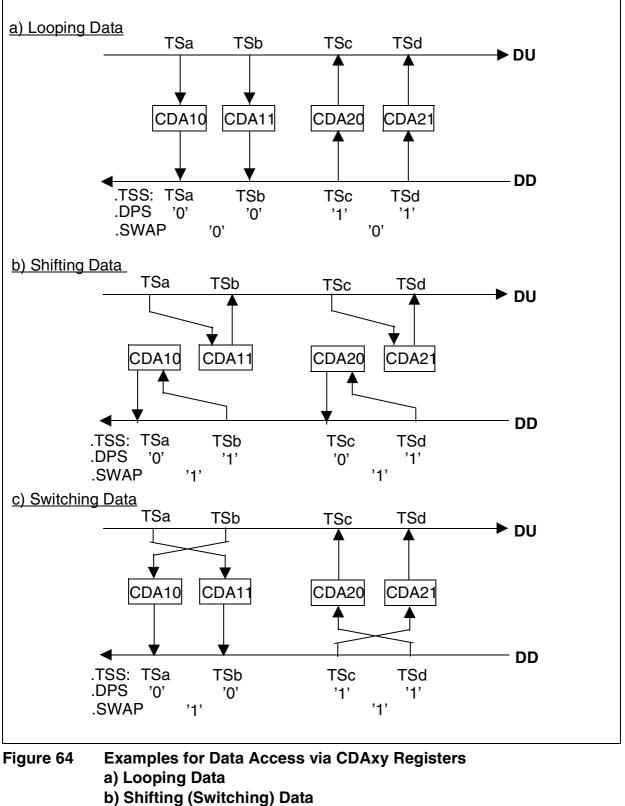

| Figure 64                                        |                                                                                   |          |

| <b>J</b>                                         | a) Looping Data                                                                   |          |

|                                                  | b) Shifting (Switching) Data                                                      |          |

|                                                  | c) Shifting and Looping Data 142                                                  |          |

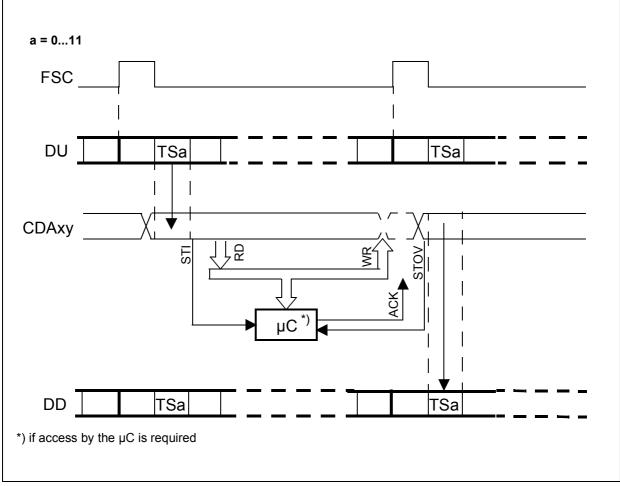

| Figure 65                                        | Data Access when Looping TSa from DU to DD                                        | 43       |

| Figure 66                                        |                                                                                   |          |

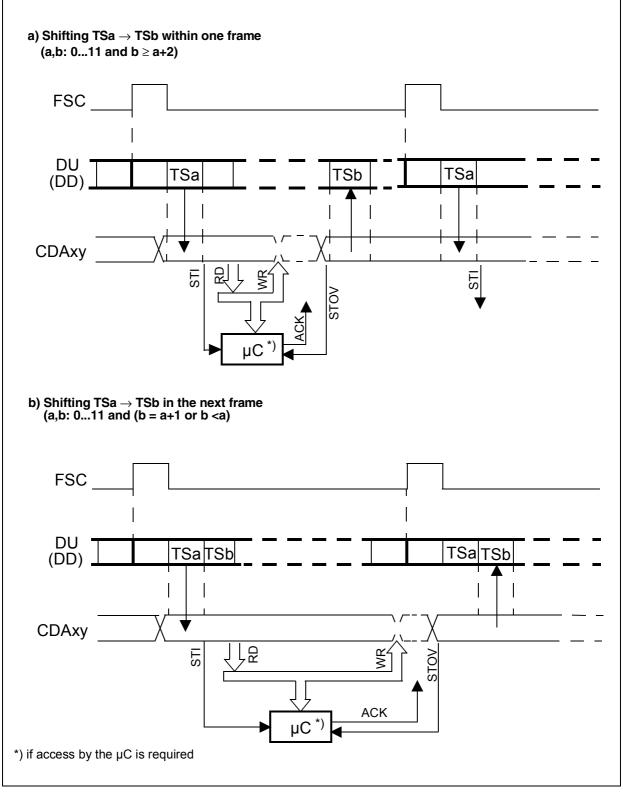

| Figure 67                                        | - · ·                                                                             |          |

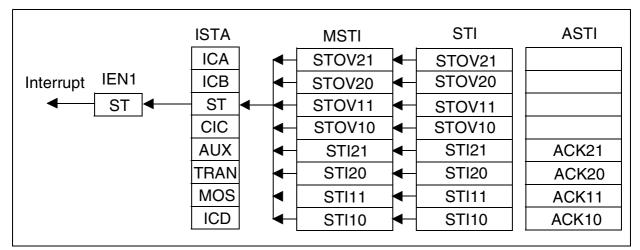

| Figure 68                                        | Interrupt Structure of the Synchronous Data Transfer                              | 47       |

| Figure 69                                        |                                                                                   |          |

|                                                  | abled STIxy 148                                                                   |          |

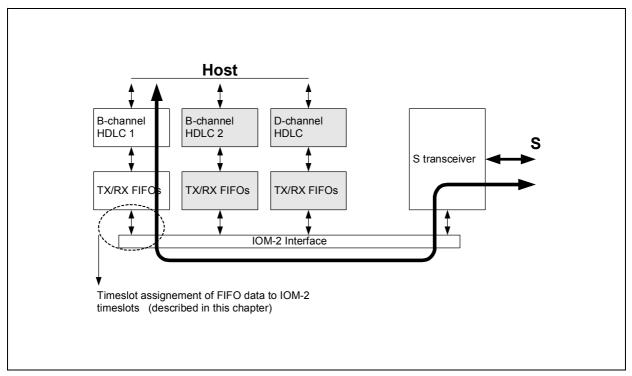

| Figure 70                                        | Timeslot Assignment on IOM-2 1                                                    | 49       |

| Figure 71                                        | Examples for HDLC Controller Access 1                                             | 50       |

#### List of Figures

#### Page

| •          |                                                                   | •   |

|------------|-------------------------------------------------------------------|-----|

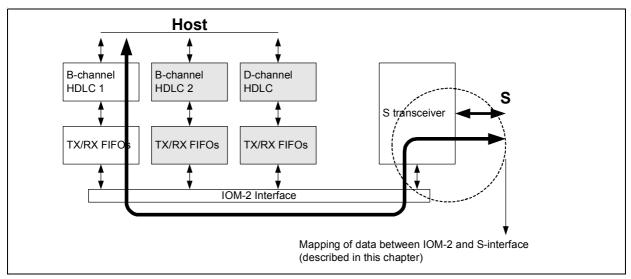

| Figure 72  | Timeslot Assignment on S                                          | 151 |

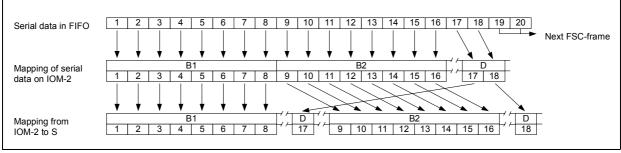

| Figure 73  | Mapping of Bits from IOM-2 to S                                   | 151 |

| Figure 74  | Data Strobe Signal.                                               |     |

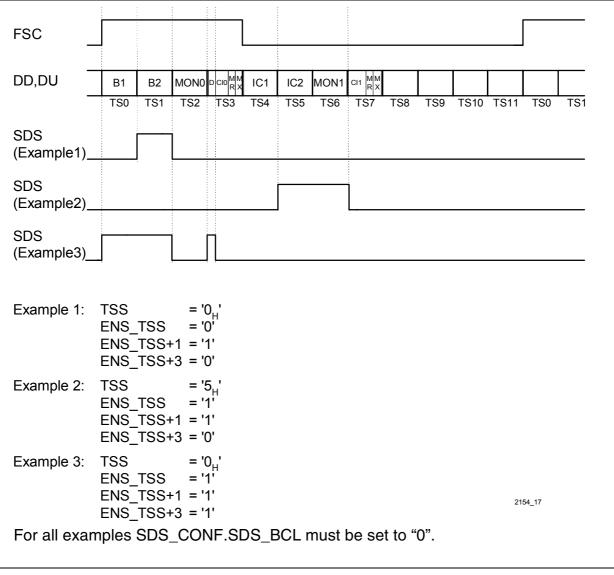

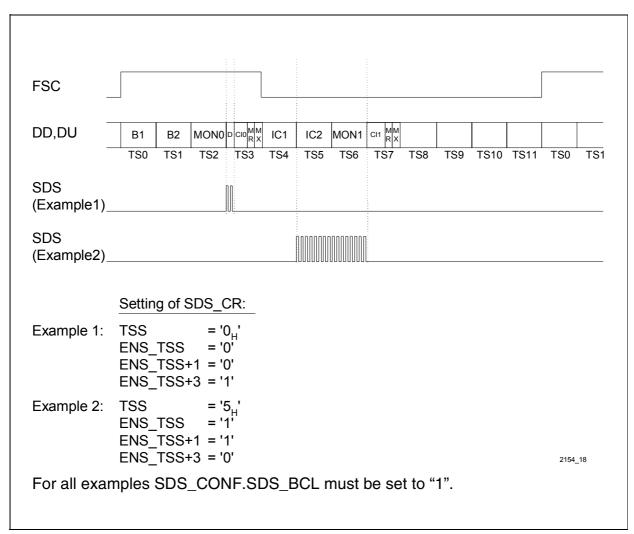

| Figure 75  | Strobed IOM-2 Bit Clock. Register SDS_CONF programmed to $01_{H}$ | 154 |

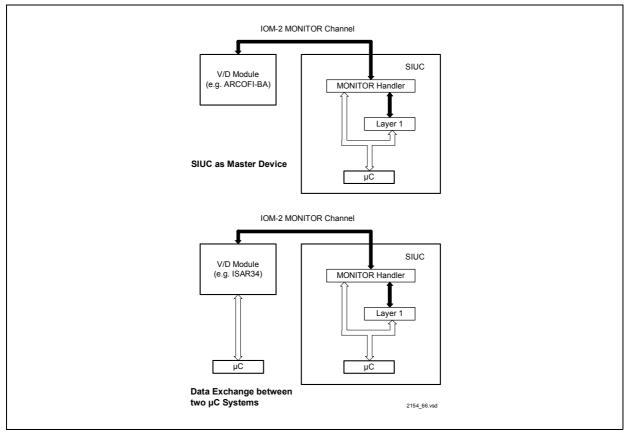

| Figure 76  | Examples of MONITOR Channel Applications in IOM-2 TE Mode         | 155 |

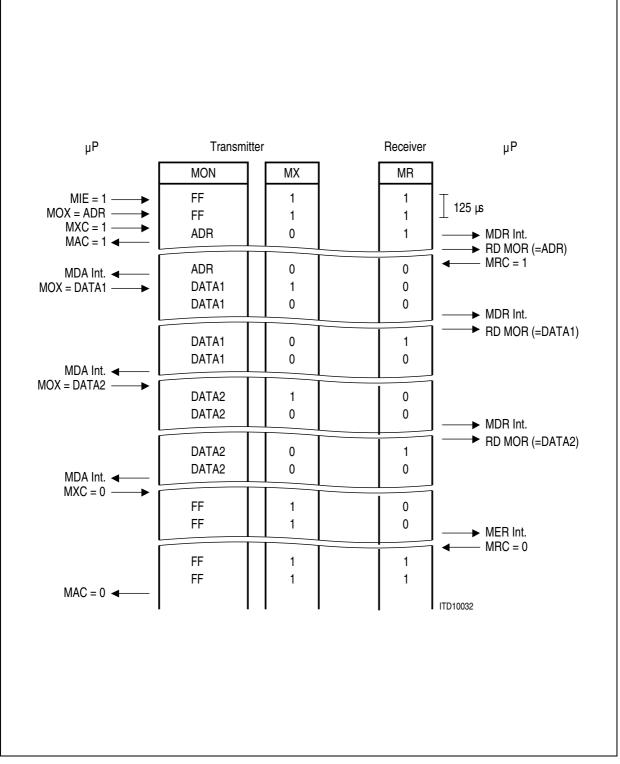

| Figure 77  | MONITOR Channel Protocol (IOM-2)                                  | 157 |

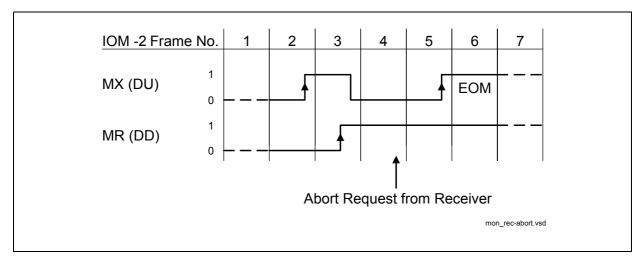

| Figure 78  | Monitor Channel, Transmission Abort requested by the Receiver     | 160 |

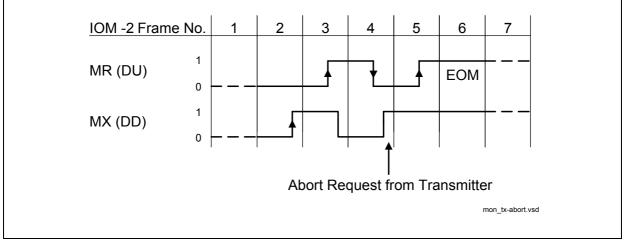

| Figure 79  | Monitor Channel, Transmission Abort requested by the Transmitter. | 160 |

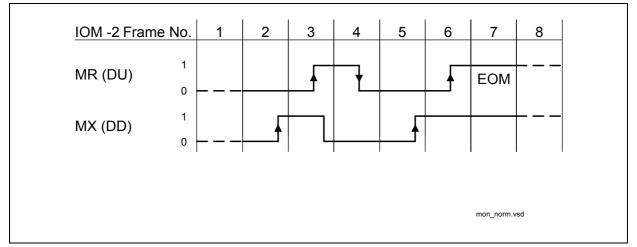

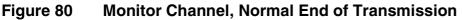

| Figure 80  | Monitor Channel, Normal End of Transmission                       | 161 |

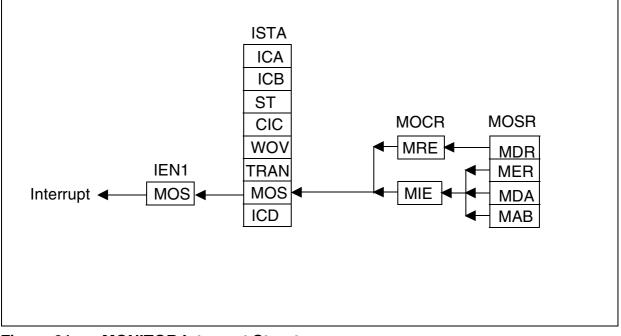

| Figure 81  | MONITOR Interrupt Structure                                       | 162 |

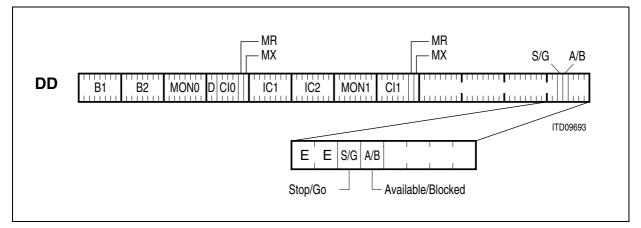

| Figure 82  | CIC Interrupt Structure                                           | 164 |

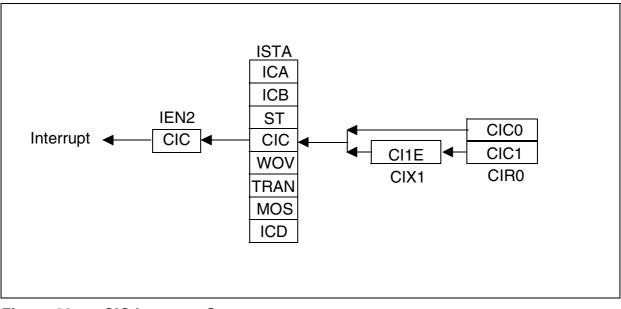

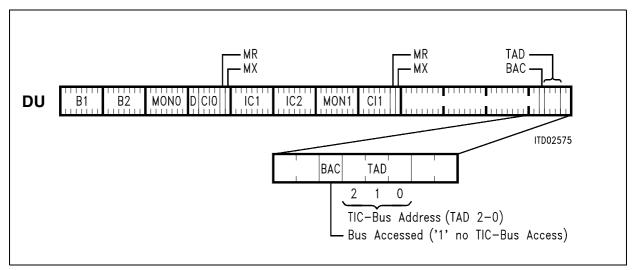

| Figure 83  | Structure of Last Octet of Ch2 on DD                              | 165 |

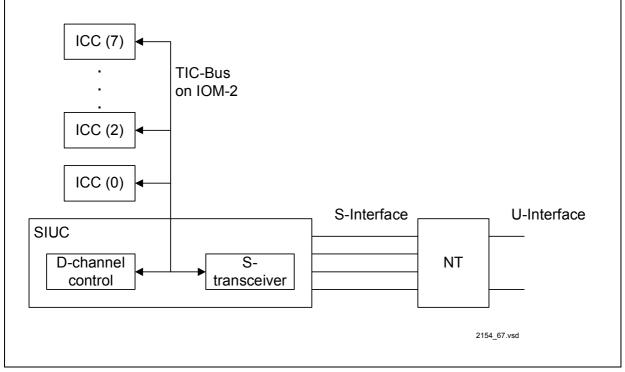

| Figure 84  | Applications of TIC Bus in IOM-2 Bus Configuration                | 166 |

| Figure 85  | Structure of Last Octet of Ch2 on DU                              | 167 |

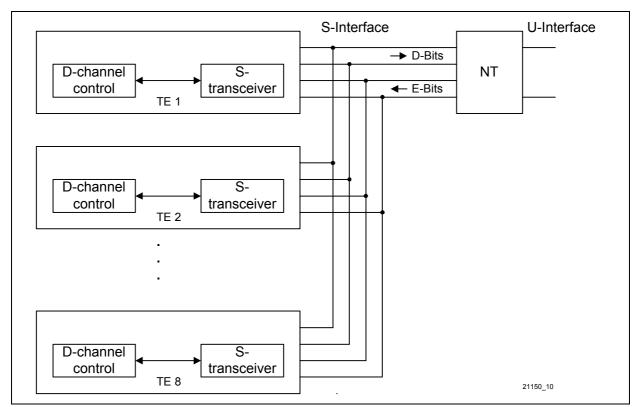

| Figure 86  | D-Channel Access Control on the S-Interface                       | 169 |

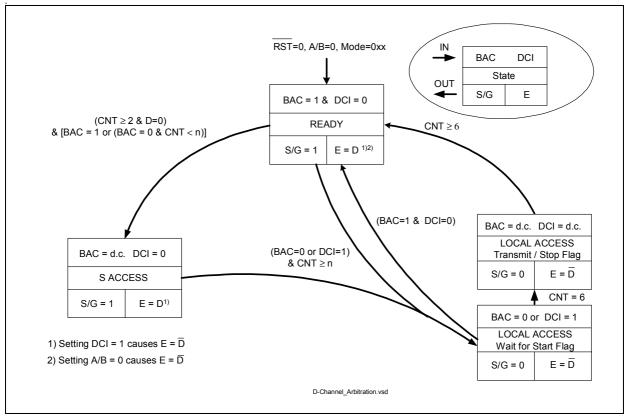

| Figure 87  | State Machine of the D-Channel Arbiter (Simplified View)          | 170 |

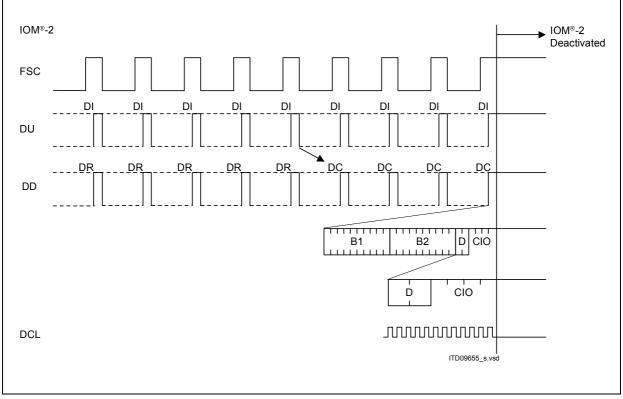

| Figure 88  | Deactivation of the IOM-2 Interface                               | 172 |

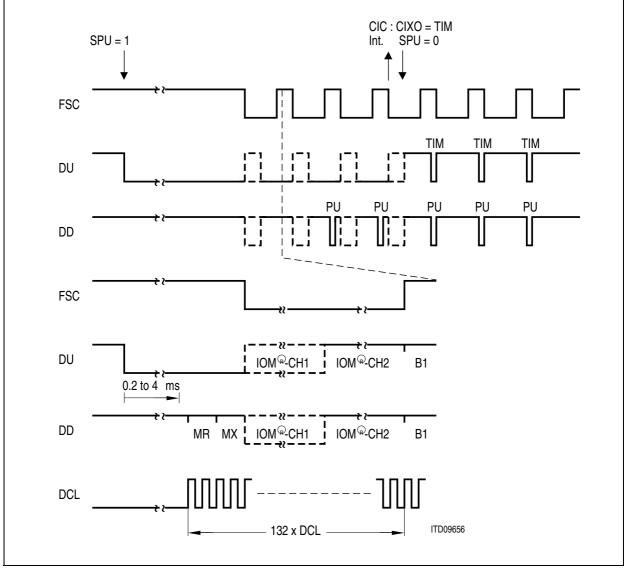

| Figure 89  | Activation of the IOM-2 interface                                 | 173 |

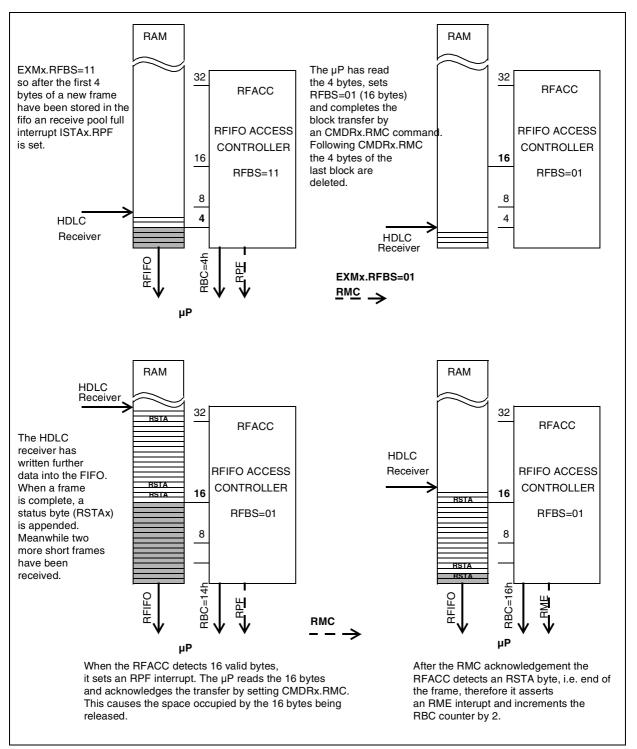

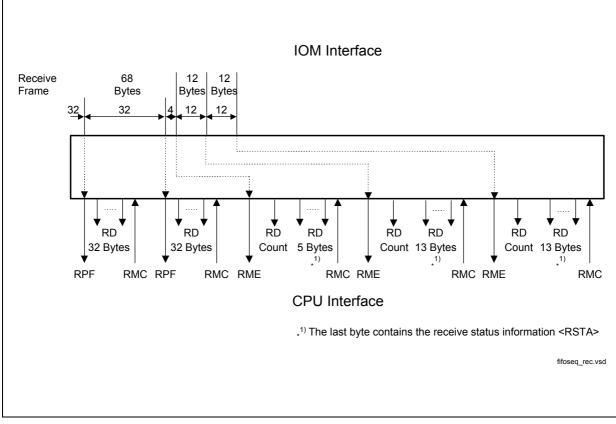

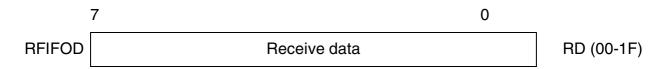

| Figure 90  | RFIFO Operation                                                   | 180 |

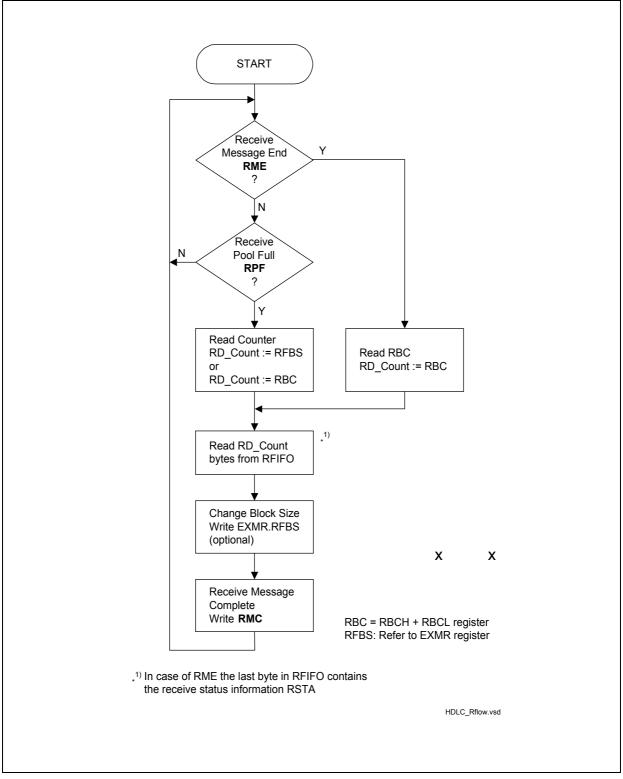

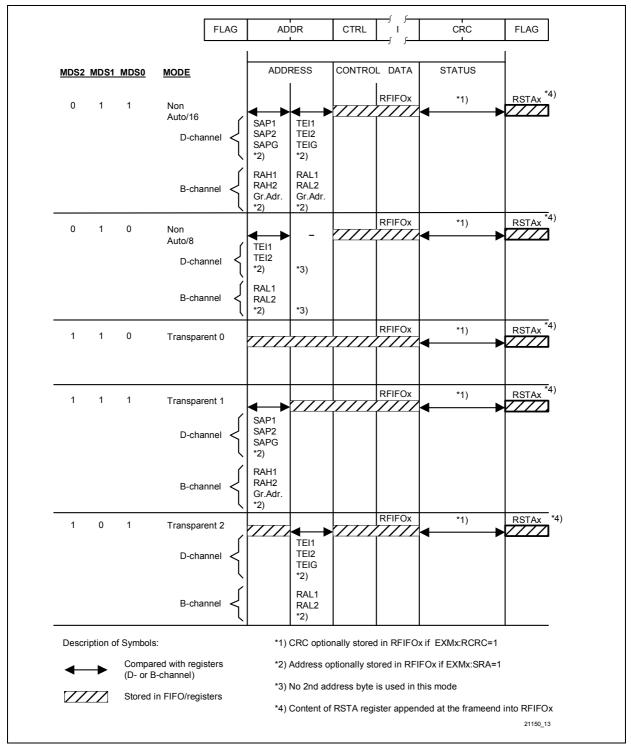

| Figure 91  | Data Reception Procedures                                         | 182 |

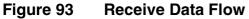

| Figure 92  | Reception Sequence Example.                                       | 183 |

| Figure 93  | Receive Data Flow                                                 | 184 |

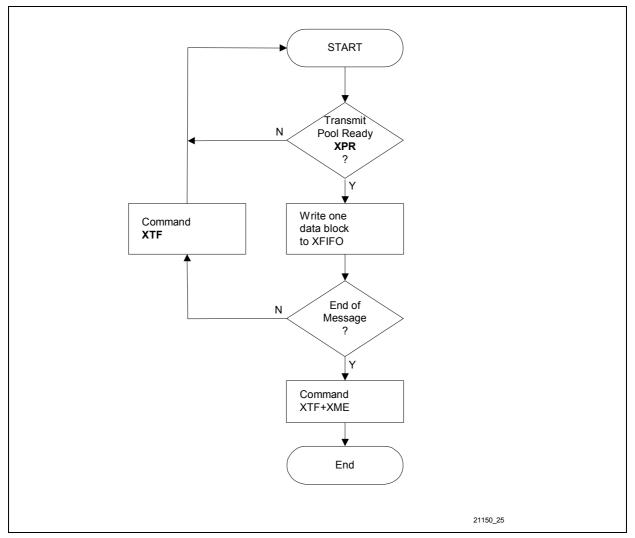

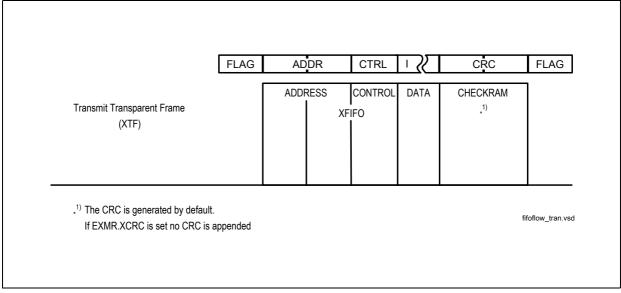

| Figure 94  | Data Transmission Procedure                                       | 189 |

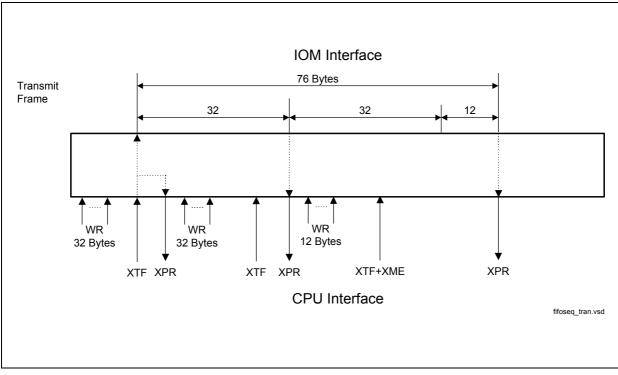

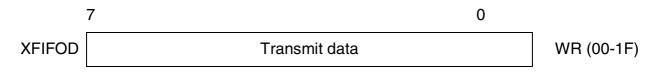

| Figure 95  | Transmission Sequence Example                                     | 190 |

| Figure 96  | Transmit Data Flow                                                | 191 |

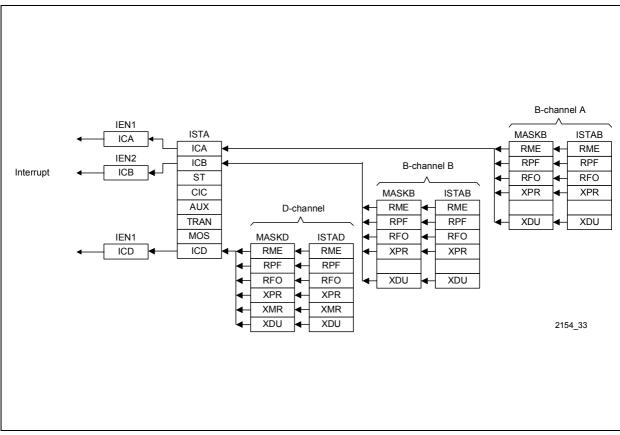

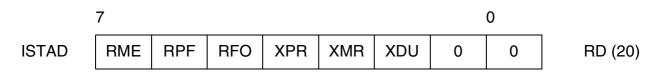

| Figure 97  | Interrupt Status Registers of the HDLC Controllers                | 193 |

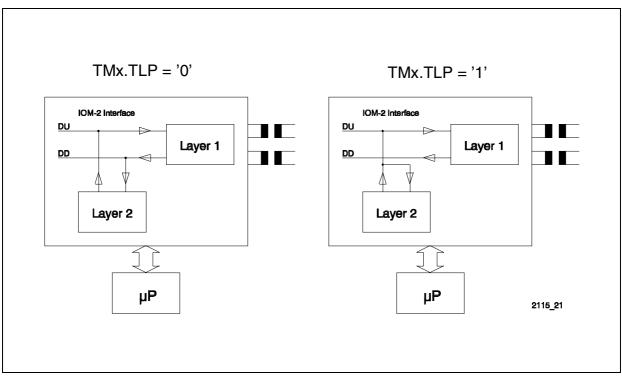

| Figure 98  | Layer 2 Test Loops                                                | 194 |

| Figure 99  | Register Mapping of the SIUC-BA                                   | 196 |

| Figure 100 | Interrupt Request Sources (Part 1) - Miscellaneous Interrupts     | 270 |

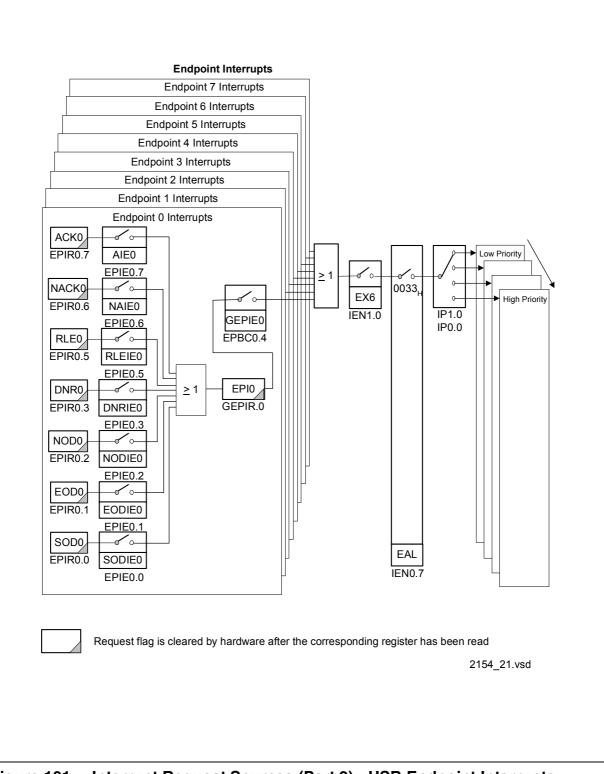

| Figure 101 | Interrupt Request Sources (Part 2) - USB Endpoint Interrupts      | 271 |

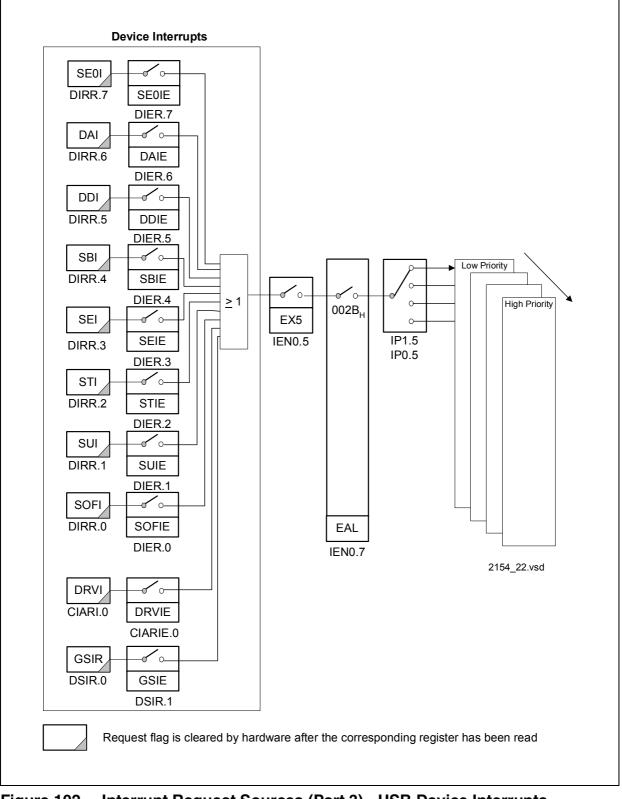

| Figure 102 | Interrupt Request Sources (Part 3) - USB Device Interrupts        | 272 |

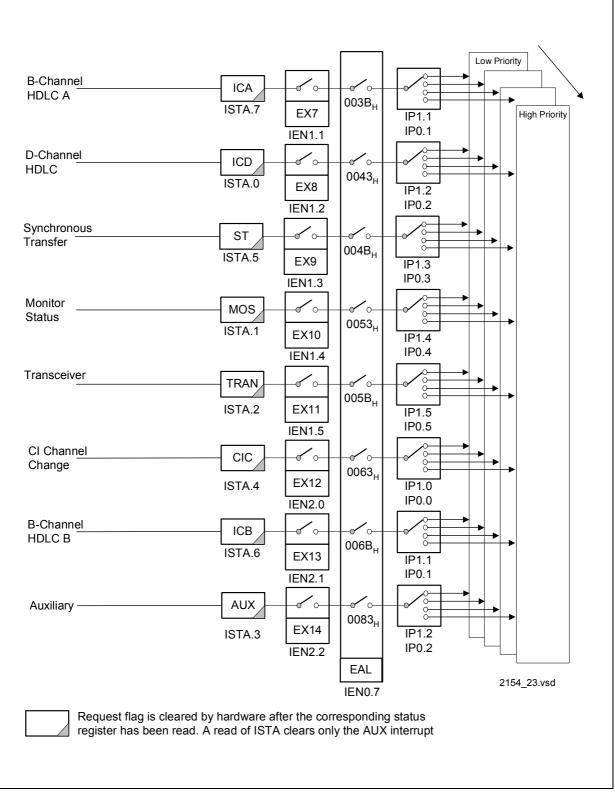

| Figure 103 | Interrupt Request Sources (Part 4) - ISDN Interrupts              | 273 |

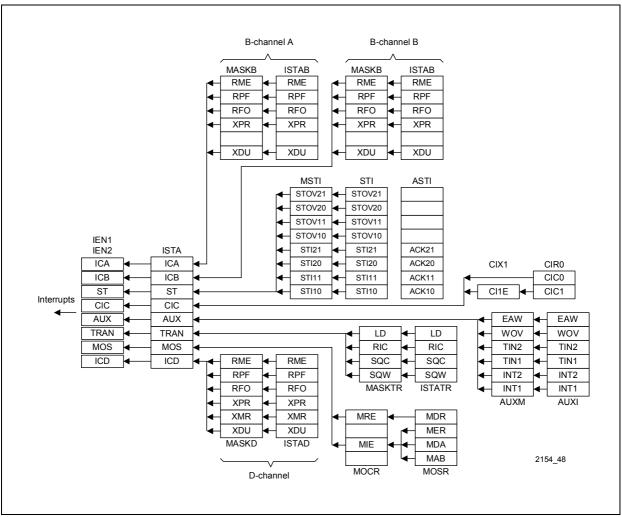

| Figure 104 | ISDN Interrupt Status Registers.                                  | 274 |

| Figure 105 | Wakeup Sources in Suspend Mode                                    | 292 |

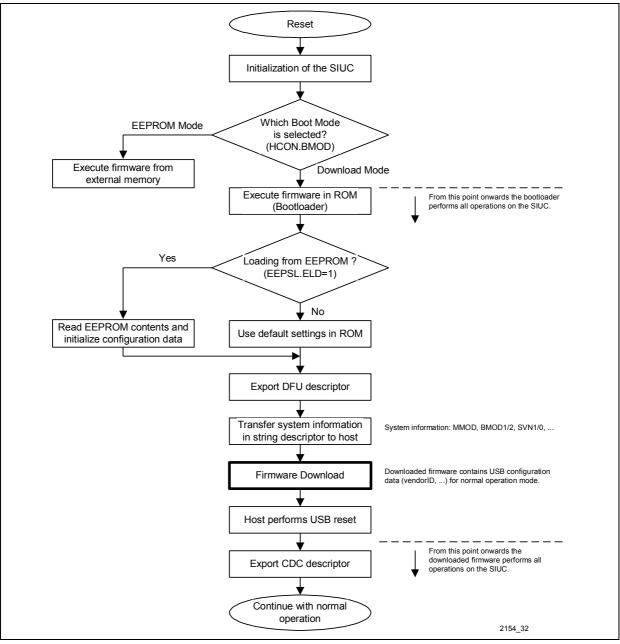

| Figure 106 | Bootmode Procedure                                                |     |

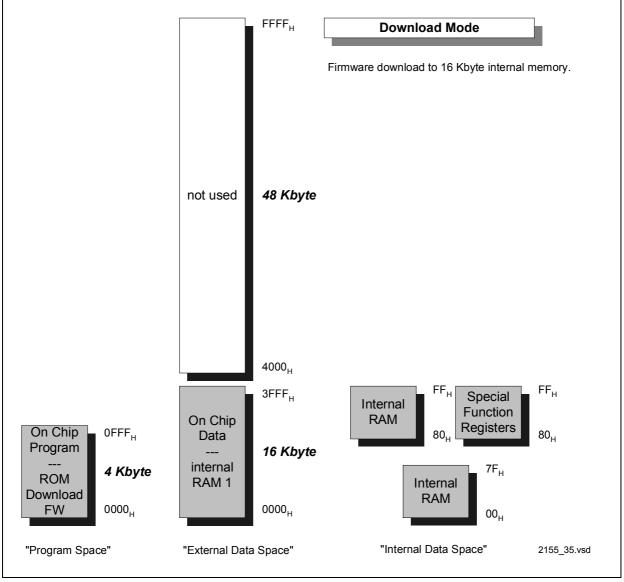

| Figure 107 | Memory Map for Firmware Download                                  | 300 |

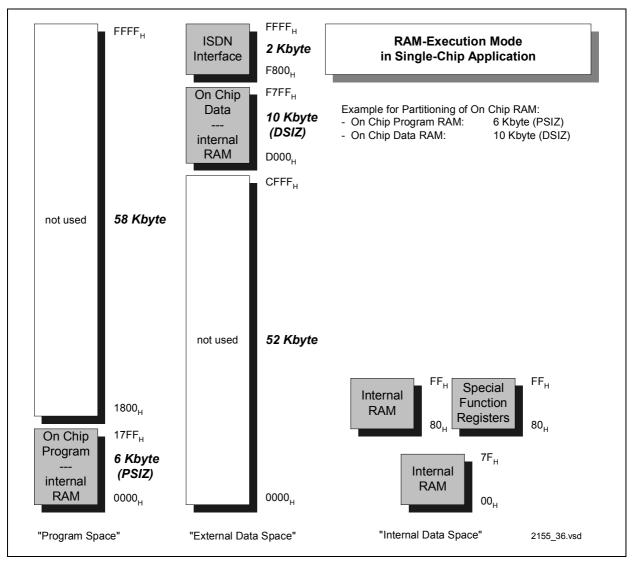

| Figure 108 | Firmware Execution in RAM                                         |     |

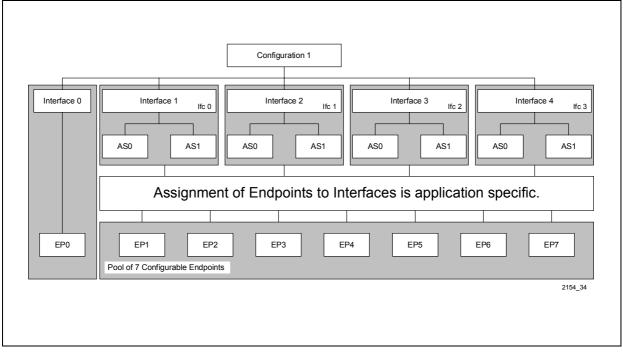

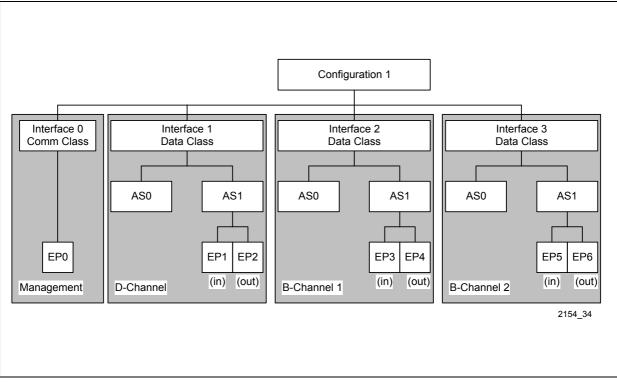

| Figure 109 | General USB Model                                                 | 302 |

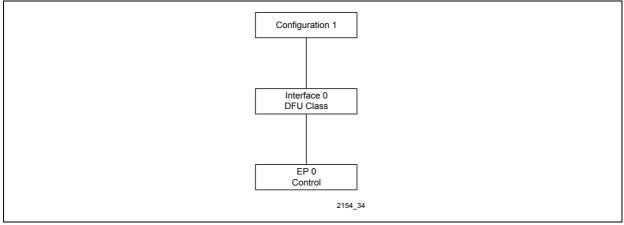

| Figure 110 | USB Configuration in DFU Mode                                     | 303 |

| Figure 111 | SIUC-BA Firmware Operation                                        | 303 |

| Figure 112 | USB Configuration in CDC Mode.                                    |     |

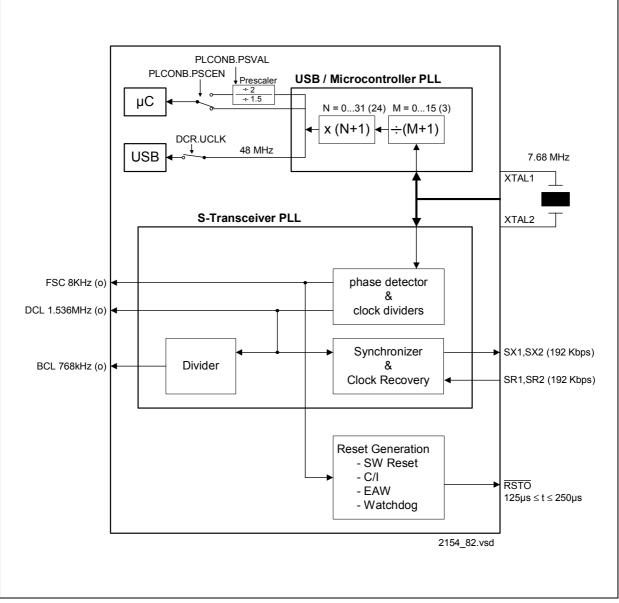

| Figure 113 | SIUC-BA Clock System                                              |     |

| List of Figure | es                                           | Page |

|----------------|----------------------------------------------|------|

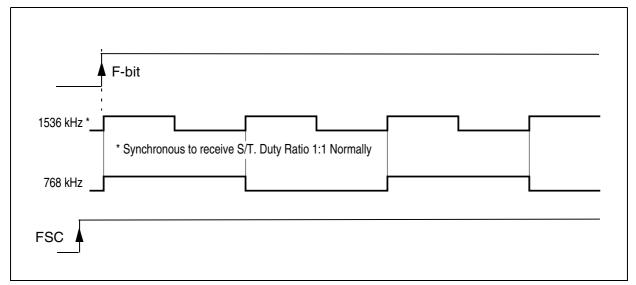

| Figure 114     | Phase Relationships of SIUC-BA Clock Signals | 315  |

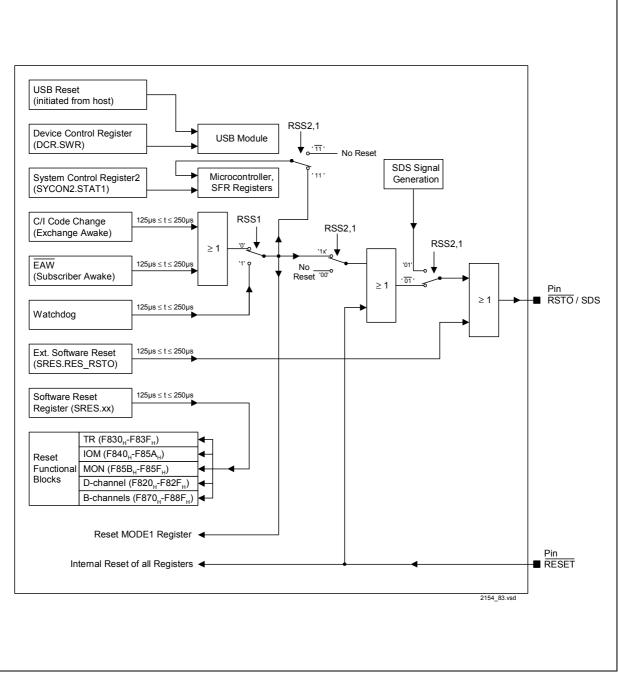

| Figure 115     | Reset Generation                             | 319  |

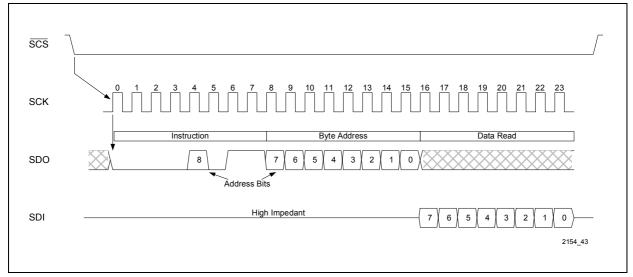

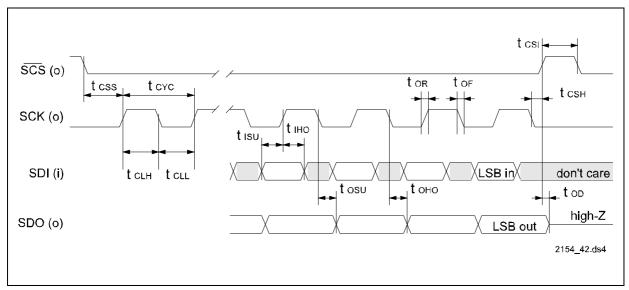

| Figure 116     | SPI Read Access                              | 322  |

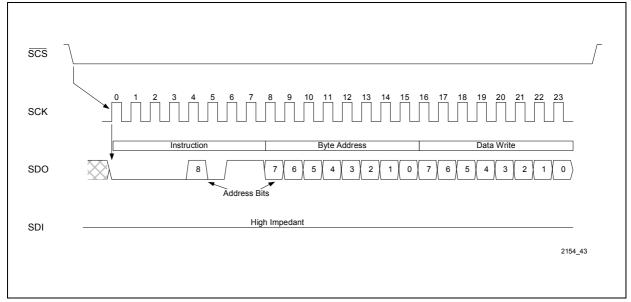

| Figure 117     | SPI Write Access                             | 323  |

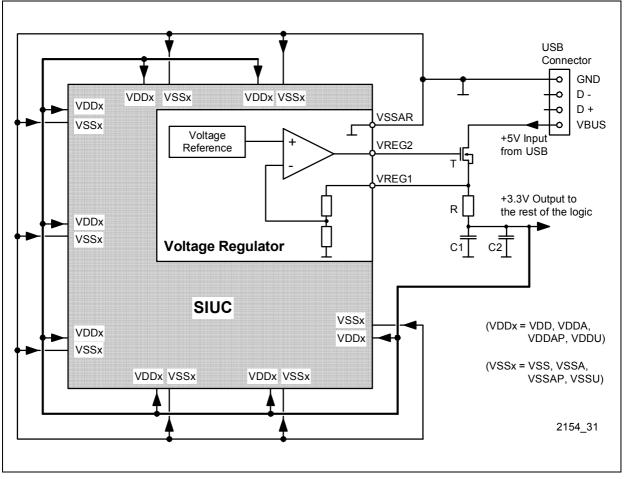

| Figure 118     | External Circuitry of the Voltage Regulator  | 328  |

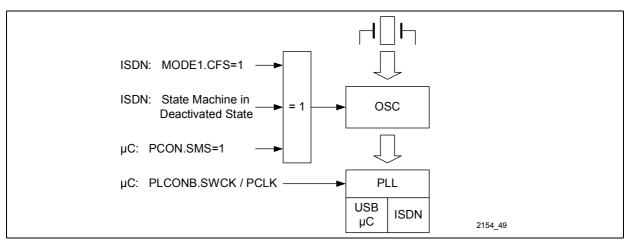

| Figure 119     | Clocks in Suspend Mode                       | 333  |

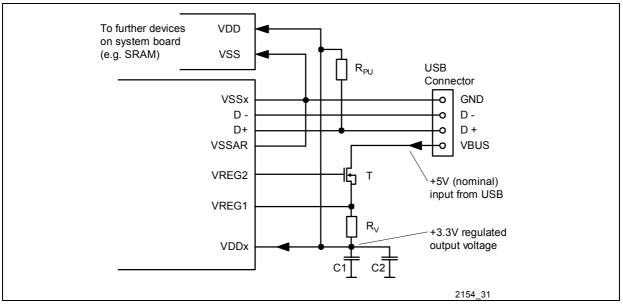

| Figure 120     | Voltage Regulator Circuit                    | 344  |

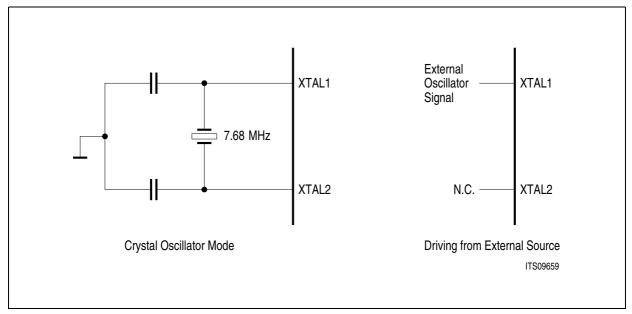

| Figure 121     | Oscillator Circuits                          | 346  |

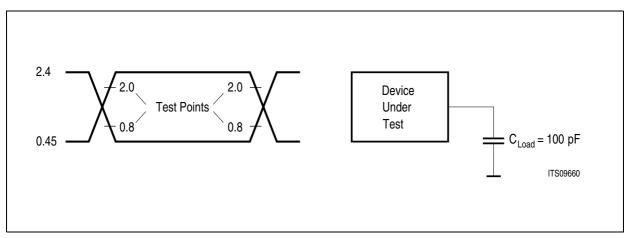

| Figure 122     | Input/Output Waveform for AC Tests           | 348  |

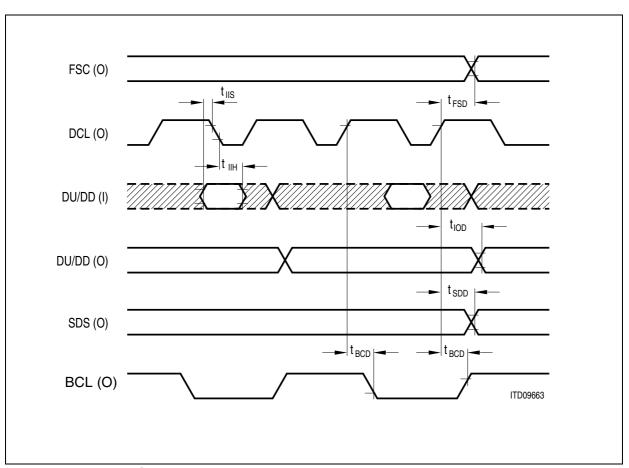

| Figure 123     | IOM® Timing (TE mode)                        | 349  |

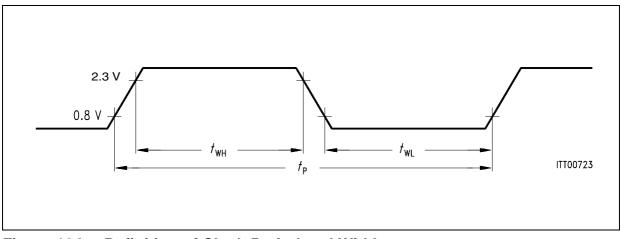

| Figure 124     | Definition of Clock Period and Width         | 350  |

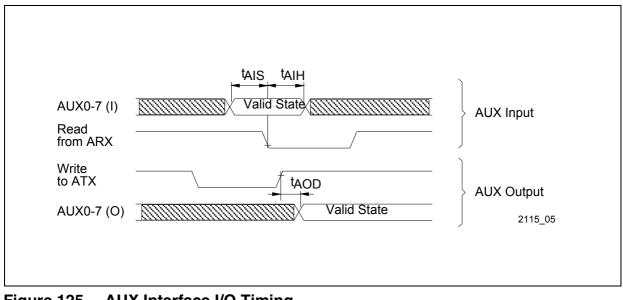

| Figure 125     | AUX Interface I/O Timing                     | 351  |

| Figure 126     | AUX Interface I/O Timing                     | 352  |

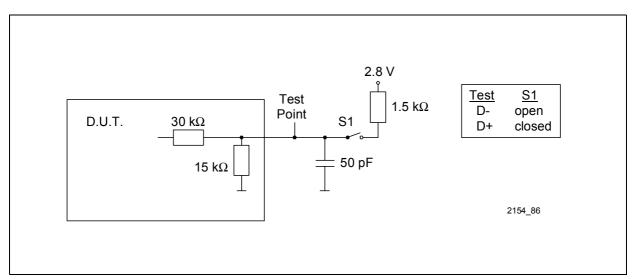

| Figure 127     | Load for D+/D                                | 353  |

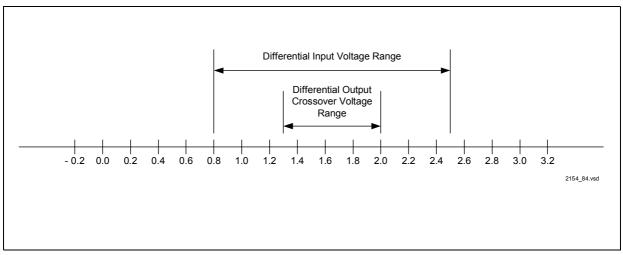

| Figure 128     | Differential Input Sensitivity Range         | 354  |

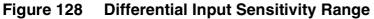

| Figure 129     | Reset Signal                                 | 354  |

| Lis | t d | of '     | Та  | bl | es |

|-----|-----|----------|-----|----|----|

|     |     | <i>.</i> | I U |    | 60 |

| Table 1  | Pin Definition - IOM-2 Interface                                | 8    |

|----------|-----------------------------------------------------------------|------|

| Table 2  | Pin Definition - Auxiliary Interface                            | 9    |

| Table 3  | Pin Definition - Miscellaneous                                  | . 12 |

| Table 4  | Pin Definition - Power Supply                                   | . 13 |

| Table 5  | Pin Definition - IOM-2 Interface                                | . 15 |

| Table 6  | Pin Definition - Auxiliary Interface                            | . 16 |

| Table 7  | Pin Definition - Miscellaneous                                  | . 16 |

| Table 8  | Special Function Registers - Functional Blocks                  | . 24 |

| Table 9  | Special Function Registers - Numerically ordered addresses      | . 27 |

| Table 10 | USB Device and Endpoint Registers                               |      |

| Table 11 | USB Transfer Modes                                              |      |

| Table 12 | Buffer Length and Base Address Values                           | . 69 |

| Table 13 | USB Configuration Block                                         |      |

| Table 14 | Bitfield Definition of USB Configuration Block                  |      |

| Table 15 | Standard Device Requests                                        |      |

| Table 16 | SIUC-BA Timers                                                  |      |

| Table 17 | S/Q-Bit Position Identification and Multiframe Structure        | 111  |

| Table 18 | Examples for Synchronous Transfer Interrupts                    | 147  |

| Table 19 | Transmit Direction                                              | 156  |

| Table 20 | Receive Direction                                               | 156  |

| Table 21 | HDLC Controller Address Range                                   | 174  |

| Table 22 | Receive Byte Count with RBC110 in the RBCHx/RBCLx registers     | 178  |

| Table 23 | Receive Information at RME Interrupt                            | 185  |

| Table 24 | XPR Interrupt (availability of XFIFOx) after XTF, XME Commands. | 187  |

| Table 25 | Interrupt Priority Order                                        | 289  |

| Table 26 | Interrupt Vectors                                               | 291  |

| Table 27 | Enabling / Disabling of Wakeup Sources                          | 293  |

| Table 28 | Boot Mode Selection                                             | 295  |

| Table 29 | SIUC-BA Configuration Data for USB Descriptors                  | 306  |

| Table 30 | Organisation of EEPROM Memory                                   |      |

| Table 31 | USB Power Consumption Limits                                    |      |

| Table 32 | IOM Clocks                                                      |      |

| Table 33 | Reset Source Selection (MODE1.RSS2,1)                           |      |

| Table 34 | AUX Pin Functions                                               |      |

|          |                                                                 |      |

# Preface

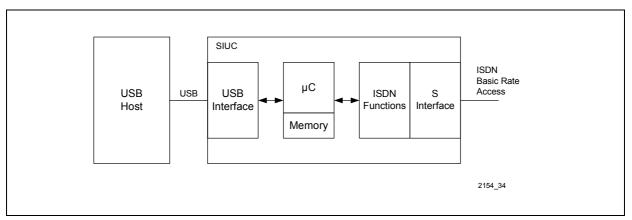

The Single Chip ISDN USB Controller - Basic (SIUC-BA) is an optimized low cost solution for host based connectivity to ISDN through USB. This document provides reference information on the features and possible applications.

# **Organization of this Document**

This Data Sheet is divided into 11 chapters. It is organized as follows:

- Chapter 1, Overview Gives a general description of the product, lists the key features, describes functional modules and presents some typical applications.

- Chapter 2, Pin Description Lists pins with associated signals, categorizes signals according to function, and describes signals.

- Chapter 3, C800 Microcontroller Describes the embedded C800 8-bit microcontroller, memory organisation and special function registers.

- Chapter 4, USB Module Covers the USB implementation on the SIUC-BA describing the transfer modes, the memory buffer operation, the USB device framework and the USB registers.

- Chapter 5, ISDN Module Includes all the modules, modes and interfaces related to ISDN, especially the IOM-2 interface, the S-transceiver and the HDLC Controllers.

- Chapter 6, Interrupt System

Describes the microcontroller interrupt sources along with all interrupt status and

interrupt enable registers, and describes interrupt priority handling.

- Chapter 7, Firmware Describes the way of running firmware, the memory map, and explains the different USB models used with the SIUC-BA.

- Chapter 8, General Features Includes the clock and reset generation within the device, the auxiliary and SPI interfaces, and the voltage regulator.

- Chapter 9, Operational Description Briefly elaborates the operational modes like active, idle, suspend etc. within the device along with the programming sequence to be followed in different modes.

- Chapter 10, Electrical Characteristics

- Chapter 11, Package Outlines

# **Related Documents**

- USB Specification V1.1, September 23, 1998

- USB Class Definitions for Communication Devices (CDC) V1.1, January 19, 1999

- USB Device Class Specification for Device Firmware Upgrade (DFU) V1.0, May 13, 1999

- ISDN PC Adapter Circuit (IPAC-X) PSB 21150, Version 1.1, Preliminary Data Sheet, 12.99

- C540U / C541U 8-Bit CMOS Microcontroller, User's Manual 11.97.

- C501 8-Bit Single-Chip Microcontroller, User's Manual 04.97

- Embedded C165 with USB, ISDN Terminal adapter and HDLC, UTAH, Data Sheet.

#### Overview

# 1 Overview

The Single Chip ISDN USB Controller - Basic (SIUC-BA) integrates all functions on a single chip for a host based ISDN S-interface access solution through USB. It is a derivate with reduced functionality of the full feature device SIUC-X PSB 2154, which combines the basic features of the ISDN PC Adapter Circuit (IPAC PSB 2115) and the C541U 8-bit Microcontroller with USB, but in 3.3 V technology. It is dedicated for pure single chip designs without memory extension and peripheral devices.

On the ISDN side, it includes the S-transceiver (Layer 1), an HDLC controller for the Dchannel and two protocol controllers for both B-channels (Layer 2). They can be used for HDLC protocol or transparent access. The FIFO size of the B-channel buffers is 128 bytes per channel and per direction.

On the USB side, it includes a full speed USB transceiver, supports bus powered operation and is compliant with USB Specification V1.1 and the Communication Device Class (CDC) Specification V1.1 for ISDN devices. The endpoints can be controlled by the microcontroller by special function registers. A boot loader in the internal ROM allows firmware download to the internal memory via USB according to the USB Device Class Specification for Device Firmware Upgrade (DFU) V1.0.

The embedded new C800 Microcontroller core (8-bit) enables transparent or HDLCframed exchange of B-channel data between the S-interface and USB. In addition, it provides lower level D-channel access control functions. The operational firmware which is downloaded via USB is contained in internal 16K RAM.

Firmware can be developed with the full feature version SIUC-X PSB 2154 using internal memory (single chip mode) or using additional external memory (shared or separate memory mode), whereby emulation is supported through Enhanced Hooks Technology<sup>TM</sup>. Emulation is not supported by the SIUC-BA.

The programmable I/O lines of the 8-bit auxiliary port may be used for external control functions and to forward status information to the  $\mu$ C. The SPI interface for serial EEPROM communication is multiplexed onto these lines. 3 programmable LED output ports are available, one of them can indicate the activation status of the S-interface automatically.

The onchip voltage regulator supports the design of bus powered applications, i.e. the regulated 3.3V supply is generated out of the USB supply by the SIUC-BA itself without requiring an external voltage regulator.

The SIUC-BA is produced in advanced CMOS technology.

# Single Chip ISDN USB Controller - Basic SIUC-BA

PSB 2155

# Version 1.3

1.1 Features

#### General

- Single chip host based ISDN solution for USB

- Derivate of SIUC-X with reduced features

- 3.3V power supply

- Programmable reset sources

- Onchip PLL for 48 MHz clock generation

- 5V tolerant I/Os

- Onchip voltage regulator for bus-powered operation (patent pending)

# ISDN (S-Interface, 2B+D Channels)

- S/T-transceiver (ITU-T I.430) operating in TE mode

- D-channel and B-channel protocol controllers (HDLC)